DDR3_SDRAM

は、コンピュータのメインメモリについてです。グラフィックメモリについては、

GDDR3を参照してモバイルメモリについては、

LPDDR3を参照してビデオゲームについては、

Dance Dance Revolution3rdMixを参照して

ダブルデータレート3同期ダイナミックランダムアクセスメモリ(DDR3 SDRAM)は、高帯域幅(「ダブルデータレート」)インターフェイスを備えた同期ダイナミックランダムアクセスメモリ(SDRAM)の一種で、2007年から使用されています。DDRおよびDDR2の高速後継、およびDDR4同期ダイナミックランダムアクセスメモリ(SDRAM)チップの前身。DDR3 SDRAMは、信号電圧、タイミング、およびその他の要因が異なるため、以前のタイプのランダムアクセスメモリ(RAM)との下位互換性も下位互換性もありません。 DDR3 SDRAM ダブルデータレート3同期ダイナミックランダムアクセスメモリ

RAMの種類

4 GB PC3-12800 ECC DDR3 DIMM

デベロッパー JEDEC タイプ

同期ダイナミックランダムアクセスメモリ(SDRAM)

世代第三世代 発売日

2007年 (2007)

基準

DDR3-800(PC3-6400)

DDR3-1066(PC3-8500)

DDR3-1333(PC3-10600)

DDR3-1600(PC3-12800)

DDR3-1866(PC3-14900)

DDR3-2133(PC3-17000)

クロックレート

400〜1066 MHz

電圧

リファレンス1.5V

前任者

DDR2 SDRAM(2003)

後継

DDR4 SDRAM(2014)

DDR3はDRAMインターフェイス仕様です。データを格納する実際のDRAMアレイは、以前のタイプと同様のパフォーマンスを備えています。DDR3SDRAMの直前のDDR2SDRAMに対する主な利点は、2倍の速度(内部メモリアレイの8倍の速度)でデータを転送できることであり、より高い帯域幅またはピークデータレートを可能にします。

DDR3規格では、最大8ギガビット(Gbit)のDRAMチップ容量、およびDDR3 DIMMあたり合計最大16ギガビット(GB)の64ビットの最大 4ランクが許可されています。2013年のIvyBridge-Eまでハードウェアの制限が修正されなかったため、ほとんどの古いIntelCPUは8GBDIMMに対して最大4Gbitチップしかサポートしません(IntelのCore 2DDR3チップセットは最大2Gbitのみをサポートします)。すべてのAMDCPUは、16 GB DDR3DIMMの完全な仕様を正しくサポートしています。

コンテンツ

1 歴史

1.1 後継

2 仕様

2.1 概要 2.2 デュアルインラインメモリモジュール 2.3 レイテンシー 2.4 消費電力 2.5 モジュール 2.62.6 シリアルプレゼンス検出

2.6.1 リリース4

2.6.2 XMP拡張機能

3 バリアント

3.1 DDR3LおよびDDR3U拡張機能

4 機能の概要

4.1 コンポーネント 4.2 モジュール 4.3 DDR2に対する技術的利点

5 も参照してください

6 ノート

7 参考文献

8 外部リンク

歴史

2005年2月、Samsungは最初のプロトタイプDDR3メモリチップを発表しました。サムスンはDDR3の開発と標準化において主要な役割を果たしました。 2005年5月、JEDEC委員会の議長であるDesi Rhodenは、DDR3は「約3年間」開発中であったと述べました。

DDR3は2007年に正式に発売されましたが、IntelのストラテジストCarlos Weissenbergによると、2008年8月の展開の初期段階で、2009年末またはおそらく2010年初頭まで売上高がDDR2を追い抜くとは予想されていませんでした。(市場浸透の同じタイムスケールは、 2007年4月の1年前にマーケットインテリジェンス会社DRAMeXchangeによって、2005年にDesi Rhodenによって述べられました。 )DDR3の使用増加の背後にある主な原動力は新しいものです。IntelのCorei7プロセッサとAMDのPhenomIIプロセッサは、どちらも内部メモリコントローラを備えています。前者はDDR3を必要とし、後者はそれを推奨します。IDCは、2009年1月に、DDR3の売上が2009年に販売されたDRAMユニット全体の29%を占め、2011年までに72%に上昇すると発表しました。

後継 DDR4 SDRAM 2012年9月、JEDECはDDR4の最終仕様をリリースしました。 DDR3と比較したDDR4の主な利点には、クロック周波数とデータ転送速度の標準化された範囲が高く 、電圧が大幅に低いことが含まれます。

仕様

概要

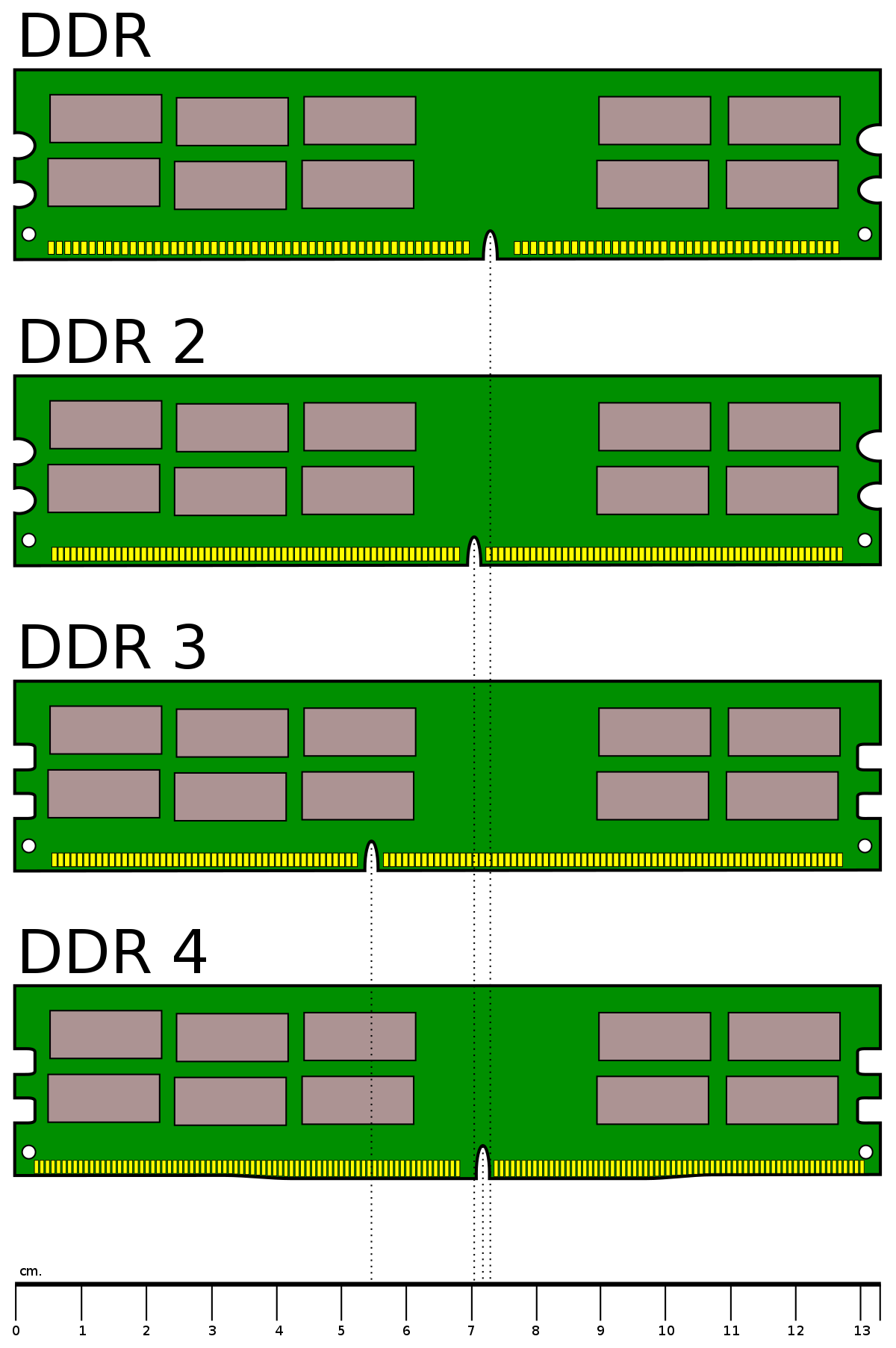

DDR、 DDR2、およびDDR3SDRAM の

物理的な比較

デスクトップPC(DIMM)

ノートブックおよびコンバーチブルPC(SO-DIMM)

DDR2メモリと比較して、DDR3メモリはより少ない電力を使用します。一部のメーカーはさらに、電流の漏れを減らすために「デュアルゲート」トランジスタを使用することを提案しています。

JEDECによると、 :111 1.575ボルトは、サーバーやその他のミッションクリティカルなデバイスなど、メモリの安定性を最優先する場合は絶対最大値と見なす必要がさらに、JEDECは、メモリモジュールが恒久的な損傷を受ける前に最大1.80ボルトに耐える必要があると述べていますが、そのレベルで正しく機能する必要はありません。 :109

もう1つの利点は、8バーストの深さのプリフェッチバッファです。対照的に、DDR2のプリフェッチバッファは4バーストディープであり、DDRのプリフェッチバッファは2バーストディープです。この利点は、DDR3の転送速度を可能にするテクノロジーです。

DDR3モジュールは、400〜1066 MHz I / Oクロックの立ち上がりエッジと立ち下がりエッジの両方を使用して、800〜2133 MT / sの速度でデータを転送できます 。これは、DDR2のデータ転送速度の2倍(200〜533 MHz I / Oクロックを使用して400〜1066 MT / s)であり、DDRの速度の4倍(100〜200 MHz I / Oクロックを使用して200〜400 MT / s)です。 。高性能グラフィックスは、フレームバッファ間の高帯域幅データ転送が必要なこのような帯域幅要件の最初の推進力でした。

ヘルツは1秒あたりのサイクル数の尺度であり、他のすべての転送よりも頻繁に信号サイクルが発生することはないため、転送速度をMHz単位で記述することは、非常に一般的ですが、技術的に正しくありません。また、さまざまなメモリタイミングがクロックサイクルの単位で指定されているため、誤解を招く可能性がこれは、データ転送の半分の速度です。

DDR3は、タイミングと電圧は異なりますが、DDRおよびDDR2と同じ電気信号規格であるスタブシリーズ終端ロジックを使用します。具体的には、DDR3はSSTL_15を使用します。

2005年2月、Samsungは、 512Mbの容量と1.066Gbpsの帯域幅を備えた最初のDDR3メモリプロトタイプをデモしました。マザーボードの形式の製品は、2007年6月に市場に登場しました。これは、最大DDR3-1600(PC3-12800)の帯域幅のDIMMを搭載したIntelのP35「Bearlake」チップセットに基づいています。 2008年11月にリリースされたIntelCore i7は、チップセットを介さずにメモリに直接接続します。Core i7、i5、およびi3 CPUは、当初DDR3のみをサポートしていました。2009年2月にリリースされたAMDのソケットAM3Phenom II X4プロセッサは、DDR3をサポートする最初のプロセッサでした(下位互換性のためにDDR2を引き続きサポートします)。

デュアルインラインメモリモジュール

DDR3デュアルインラインメモリモジュール(DIMM)には240ピンがあり、DDR2と電気的に互換性がありません。DDR2DIMMとDDR3DIMMで異なる位置にあるキーノッチは、誤ってそれらを交換することを防ぎます。キーが異なるだけでなく、DDR2の側面には丸いノッチがあり、DDR3モジュールの側面には正方形のノッチが DDR3SO -DIMMには204ピンが

Skylakeマイクロアーキテクチャ用に、IntelはUniDIMMという名前のSO-DIMMパッケージも設計しました。これは、DDR3またはDDR4チップのいずれかを使用できます。その後、CPUの統合メモリコントローラはどちらでも動作します。UniDIMMの目的は、DDR3からDDR4への移行を処理することです。この場合、価格と可用性により、RAMタイプの切り替えが望ましい場合がUniDIMMの寸法とピン数は通常のDDR4SO-DIMMと同じですが、互換性のないDDR4 SO-DIMMソケットで誤って使用しないように、ノッチの配置が異なります。

レイテンシー

DDR3レイテンシは、測定されるI / Oバスクロックサイクルが短いため、数値的に高くなります。実際の時間間隔はDDR2レイテンシーと同様で、約10nsです。DDR3は通常、より新しい製造プロセスを使用するため、いくつかの改善がありますが、これはDDR3への変更によって直接引き起こされるものではありません。

CASレイテンシ(ns)= 1000×CL(サイクル)÷クロック周波数(MHz)= 2000×CL(サイクル)÷転送速度(MT / s)

JEDEC DDR2-800デバイスの一般的な遅延は5-5-5-15(12.5 ns)でしたが、JEDEC DDR3デバイスの標準的な遅延にはDDR3-1066(13.125 ns)の7-7-7-20と8が含まれます。 DDR3-1333(12 ns)の場合は8-8-24。

以前の世代のメモリと同様に、初期バージョンのリリース後、より高速なDDR3メモリが利用可能になりました。レイテンシー(9 ns)が9-9-9-28のDDR3-2000メモリは、2008年後半のIntel Core i7リリースに合わせて利用可能になりました。その後の開発により、DDR3-2400が広く利用可能になりました(CL 9– 12サイクル= 7.5〜10 ns)、最大DDR3-3200の速度が利用可能です(CL13サイクル= 8.125 ns)。

消費電力

個々のSDRAMチップ(または、拡張によりDIMM)の消費電力は、速度、使用タイプ、電圧などの多くの要因によって異なります。DellのPower Advisorは、4 GB ECC DDR1333RDIMMがそれぞれ約4Wを使用すると計算しています。対照的に、より近代的な主流のデスクトップ指向のパーツ8 GB、DDR3 / 1600 DIMMは、大幅に高速であるにもかかわらず、定格は2.58Wです。

モジュール

標準のDDR3SDRAMモジュールのリスト

名前 チップ バス タイミング

標準 タイプ モジュール クロックレート (MHz) サイクルタイム(ns)

クロックレート(MHz) 転送速度 (MT / s) 帯域幅 (MB /秒) CL-T RCD -T RP

CASレイテンシ (ns)

DDR3-800 D

PC3-6400100 10 400 800 6400

5-5-5 12.5 E 6-6-6 15

DDR3-1066 EPC3-8500 133⅓ 7.5 533⅓ 1066⅔ 8533⅓

6-6-6 11.25 F 7-7-7 13.125

G 8-8-8 15

DDR3-1333 F *PC3-10600 166⅔ 6 666⅔ 1333⅓ 10666⅔

7-7-7 10.5 G 8-8-8 12

H 9-9-9 13.5

J * 10-10-10 15

DDR3-1600 G *

PC3-12800200 5 800 1600 12800

8-8-8 10 H 9-9-9 11.25

J 10-10-10 12.5

K 11-11-11 13.75

DDR3-1866 DDR3-1866J * DDR3-1866K DDR3-1866L DDR3-1866M *PC3-14900 233⅓ 4.286

0933⅓ _1866⅔ 14933⅓

10-10-10 11-11-11 12-12-12 13-13-13

10.56 11.786 12.857 13.929

DDR3-2133 DDR3-2133K * DDR3-2133L DDR3-2133M DDR3-2133N *PC3-17000 266⅔ 3.75 1066⅔ 2133⅓ 17066⅔

11-11-11 12-12-12 13-13-13 14-14-14

10.313 11.25 12.188 13.125

*オプション

DDR3-xxxはデータ転送速度を示し、DDRチップを表しますが、PC3-xxxxは理論上の帯域幅(最後の2桁が切り捨てられたもの)を表し、組み立てられたDIMMを表すために使用されます。帯域幅は、1秒あたりの転送数に8を掛けて計算されます。これは、DDR3メモリモジュールが64データビット幅のバスでデータを転送し、1バイトが8ビットで構成されているため、転送ごとに8バイトのデータに相当するためです。

4倍のクロック信号のサイクルごとに2つの転送を使用すると、64ビット幅のDDR3モジュールは、メモリクロック速度の最大64倍の転送速度を達成できます。DDR3 SDRAMは、メモリモジュールごとに一度に64ビットずつデータが転送されるため、(メモリクロックレート)×4(バスクロックマルチプライヤの場合)×2(データレートの場合)×64(転送されるビット数)/ 8の転送レートを提供します。 (1バイトのビット数)。したがって、100 MHzのメモリクロック周波数で、DDR3SDRAMは6400MB / sの最大転送速度を提供します。

DDRメモリのデータレートが2倍になるため、データレート(MT / s)はI / Oバスクロック(MHz)の2倍になります。上で説明したように、MB /秒単位の帯域幅は、データレートに8を掛けたものです。

CL – CASレイテンシ クロックサイクル、メモリへの列アドレスの送信とそれに応じたデータの開始の間

tRCD –行のアクティブ化と読み取り/書き込みの間のクロックサイクル

tRP –行のプリチャージとアクティブ化の間のクロックサイクル

小数部の周波数は通常切り捨てられますが、正確な数値が6662/3であり、最も近い整数に丸められるため、667に切り上げられるのが一般的です。一部のメーカーは、特定の精度に丸めたり、代わりに切り上げたりします。たとえば、PC3-10666メモリはPC3-10600またはPC3-10700としてリストされます。

注:上記のすべてのアイテムは、JEDECによってJESD79-3Fとして指定されています。 :157–165 これらのリストされた仕様の間またはそれ以上のすべてのRAMデータレートは、JEDECによって標準化され多くの場合、これらは、より高い許容誤差または過電圧チップを使用したメーカーの最適化です。これらの非標準仕様のうち、到達した報告された最高速度は、2010年5月の時点でDDR3-2544と同等でした。

代替の命名: DDR3モジュールは、マーケティング上の理由から、接頭辞PC(PC3ではなく)で誤ってラベル付けされ、その後にデータレートが続くことがよくこの規則では、PC3-10600はPC1333としてリストされています。

シリアルプレゼンス検出

DDR3メモリはシリアルプレゼンス検出を利用します。シリアルプレゼンス検出(SPD)は、シリアルインターフェイスを使用してコンピュータのメモリモジュールに関する情報に自動的にアクセスするための標準化された方法です。これは通常、メモリモジュールの自動構成のための電源投入時自己診断時に使用されます。

リリース4

DDR3シリアルプレゼンス検出(SPD)ドキュメントのリリース4(SPD4_01_02_11)は、負荷軽減DIMM、および16b-SO-DIMMと32b-SO-DIMMのサポートを追加します。

JEDEC Solid State Technology Associationは、2011年9月1日にDDR3シリアルプレゼンス検出(SPD)ドキュメントのリリース4の公開を発表しました。

XMP拡張機能

Intel Corporationは、2007年3月23日にeXtreme Memory Profile(XMP )仕様を正式に発表し、DDR3SDRAMの従来のJEDECSPD仕様に対する熱狂的なパフォーマンス拡張を可能にしました。

バリアント

帯域幅の指定(DDR3-800Dなど)および容量のバリエーションに加えて、モジュールは次のいずれかになります。

マイナーエラーを修正し、信頼性を高めるためにメジャーエラーを検出するために使用される追加のデータバイトレーンを備えたECCメモリ。ECCを備えたモジュールは、指定に追加のECCまたはEによって識別されます。例:「PC3-6400ECC」またはPC3-8500E。

レジスターまたはバッファード・メモリー。これは、レジスターで信号を電気的にバッファーすることにより、シグナル・インテグリティ(したがって潜在的にクロックレートと物理スロット容量)を改善しますが、待ち時間が長くなります。これらのモジュールは、PC3-6400Rのように、指定に追加のRで識別されます。

登録されていない(別名「バッファなし」)RAMは、指定にUを追加することで識別できます。

FまたはFBで指定され、他のクラスと同じノッチ位置を持たない、完全にバッファリングされたモジュール。完全にバッファリングされたモジュールは、登録済みモジュール用に作成されたマザーボードでは使用できません。また、ノッチ位置が異なるため、物理的に挿入できません。

LRによって指定され、登録/バッファリングされたメモリに類似した負荷軽減モジュールは、LRDIMMモジュールがすべての信号の並列性を維持しながら、制御ラインとデータラインの両方をバッファリングする方法で行われます。そのため、LRDIMMメモリは全体として大きな最大メモリ容量を提供すると同時に、シリアル信号形式とパラレル信号形式の間で必要な変換によって引き起こされるFBメモリのパフォーマンスと消費電力の問題の一部に対処します。

FBDIMM(完全にバッファリングされた)メモリタイプとLRDIMM(負荷が軽減された)メモリタイプはどちらも、主にメモリチップとの間でいつでも流れる電流の量を制御するように設計されています。それらは登録済み/バッファリングされたメモリと互換性がなく、それらを必要とするマザーボードは通常、他の種類のメモリを受け入れません。

DDR3LおよびDDR3U拡張機能

DDR3L(DDR3低電圧)規格は、低電圧デバイスを指定するJESD79-3DDR3メモリデバイス規格の補遺です。 DDR3L規格は1.35Vで、モジュールにはPC3Lというラベルが付いています。例としては、DDR3L-800(PC3L-6400)、DDR3L-1066(PC3L-8500)、DDR3L-1333(PC3L-10600)、およびDDR3L-1600(PC3L-12800)がDDR3LおよびDDR3U仕様に指定されたメモリは、元のDDR3標準と互換性があり、低電圧または1.50 Vのいずれかで動作できます。ただし、モバイルを使用するシステムなど、1.35Vで動作するDDR3Lを明示的に必要とするデバイス第4世代IntelCoreプロセッサのバージョンは、1.50 VDDR3メモリと互換性がありません。 DDR3Lは、 LPDDR3モバイルメモリ規格とは異なり、互換性がありません。

DDR3U (DDR3 U ltra Low Voltage)規格は1.25 Vで、モジュールのラベルはPC3Uです。

JEDEC Solid State Technology Associationは、2010年7月26日にJEDEC DDR3L を、2011年10月にDDR3Uを公開したことを発表しました。

機能の概要

コンポーネント

非同期RESETピンの導入

システムレベルの飛行時間補正のサポート

On – DIMMミラー対応DRAMピン配列

クロックビンごとのCWL(CAS書き込みレイテンシ)の導入

オンダイI / Oキャリブレーションエンジン

読み取りおよび書き込みキャリブレーション

動的ODT(On-Die-Termination)機能により、読み取りと書き込みで異なる終了値が可能になります

モジュール

オンDIMM終端を備えたフライバイコマンド/アドレス/制御バス

高精度校正抵抗器

下位互換性がありません —DDR3モジュールはDDR2ソケットに適合しません。それらを強制すると、DIMMおよび/またはマザーボードが損傷する可能性があります

DDR2に対する技術的利点

最大2133MT / sの標準化されたより高い帯域幅パフォーマンス

ナノ秒単位で測定した場合、レイテンシがわずかに改善されました

低電力でのより高いパフォーマンス(ラップトップでのより長いバッテリー寿命)

強化された低電力機能

も参照してください

デバイス帯域幅のリスト

低電力DDR3SDRAM(LPDDR3)

マルチチャネルメモリアーキテクチャ

ノート

^ リビジョンFの前に、規格は1.975Vが絶対最大DC定格であると述べていました。

参考文献

^ カトレス、イアン(2014-02-11)。「私は16GBの未登録DDR3モジュールをリリースするインテリジェントメモリです」。anandtech.com 。

^ “”サムスンは世界初のDDR3メモリプロトタイプを実証します””。Phys.org。2005年2月17日。

^ 「2000年から2009年までの私たちの誇り高い遺産」。サムスンセミコンダクター。サムスン。

^ Sobolev、Vyacheslav(2005-05-31)。「JEDEC:途中のメモリ規格」。DigiTimes.com。2013年4月13日にオリジナルからアーカイブされました。JEDECはすでにDDR3規格の開発に順調に進んでおり、私たちは約3年間取り組んできました。歴史的なモデルに従って、あなたが持っているのと同じ3年間の新しいテクノロジーへの移行を合理的に期待できます。標準メモリの最後の数世代で見られる

^ “”IDF:”” DDR3は2009年中にDDR2に追いつきません”” “”。pcpro.co.uk。2008年8月19日。2009年4月2日のオリジナルからアーカイブ。

^ ブライアン、ガーディナー(2007年4月17日)。「DDR3メモリは2009年まで主流にはなりません」。ExtremeTech.com 。

^ ソールズベリー、アンディ(2009-01-20)。「新しい50nmプロセスにより、今年はDDR3がより高速で安価になります」。MaximumPC.com 。

^ 「JEDECはDDR4標準の公開を発表しました–JEDEC」。JEDEC 。

^ シロフ、アントン(2010年8月16日)。「4.266GHzに到達する次世代DDR4メモリ–レポート」。XbitLabs.com。2010年12月19日にオリジナルからアーカイブされました。

^ McCloskey、Alan、Research:DDR FAQ 、 2007-11-12にオリジナルからアーカイブ、2007-10-18を取得

^ “”DDR3 SDRAM標準(リビジョンF)””。JEDEC。2012年7月。

^ 「DDR3SDRAM規格(リビジョンE)」(PDF)。JEDEC。2010年7月。

^ Chang、Jaci(2004)。「DDR3メモリサブシステムの設計上の考慮事項」(PDF)。ジェデックス。p。4. 2012年7月24日にオリジナル(PDF)からアーカイブされました。

^ Soderstrom、Thomas(2007-06-05)。「パイプの夢:6つのP35-DDR3マザーボードの比較」。トムスハードウェア。

^ Fink、Wesley(2007-07-20)。「スーパータレント&チーム:DDR3-1600が登場!」。AnandTech。

^ DocMemory(2007-02-21)。「メモリモジュール画像2007」。2017年6月6日にオリジナルからアーカイブされました。2022-01-05を取得。

^ 「204ピンDDR3SDRAMアンバッファSODIMM設計仕様」。JEDEC。2014年5月。

^ 「インテルが主流のDDR3とDDR4の間でどのように移行する予定か」。techpowerup.com 。

^ シロフ、アントン(2008-10-29)。「キングストンは、Intel Corei7プラットフォーム向けの業界初の2GHzメモリモジュールを発表しました」。Xbitラボラトリーズ。2008年11月1日にオリジナルからアーカイブされました。

^ 「DellEnergySmartSolutionAdvisor」。Essa.us.dell.com。2013年8月1日にオリジナルからアーカイブされました。

^ http://www.kingston.com/dataSheets/KVR16N11_8.pdf ^ サイクルタイムは、I / Oバスクロック周波数の逆数です。たとえば、1 /(100 MHz)=クロックサイクルあたり10ns。

^ Pc310600とpc310666の違いは何ですか– New-System-Build、Tomshardware.com 、取得済み2012-01-23

^ Kingstonの2,544MHz DDR3 On Show at Computex 、 News.softpedia.com、2010-05-31、2012-01-23を取得

^ 重要な価値CT2KIT51264BA1339PC1333 4GBメモリRAM(DDR3、CL9)小売、www.amazon.co.uk、2016-05-10 、取得済み2016-05-10

^ 「DDR3シリアルプレゼンス検出(SPD)テーブルについて」。simmtester.com 。

^ 「JEDECはDDR3シリアルプレゼンス検出仕様のリリース4の公開を発表しました」。

^ 「IntelExtremeメモリプロファイル(Intel XMP)DDR3テクノロジ」(PDF)。

^ メモリテクノロジの進化:システムメモリテクノロジの概要(PDF)、Hewlett-Packard、p。18、 2011年7月24日にオリジナル(PDF)からアーカイブ

^ “LR-DIMM、LRDIMMメモリとは何ですか?(Load-Reduce DIMM)”。simmtester.com 。

^ 「JESD79-3の補遺No.1-1.35 V DDR3L-800、DDR3L-1066、DDR3L-1333、DDR3L-1600、およびDDR3L-1866」。2013年5月。

^ 「JESD79-3の補遺No.1-1.35 V DDR3L-800、DDR3L-1066、DDR3L-1333、DDR3L-1600、およびDDR3L-1866」。2013年5月。DDR3L VDD / VDDQ要件-電源:DDR3L動作= 1.283 V〜1.45 V; DDR3動作= 1.425 V〜1.575 V .. DDR3L動作用に初期化されると、DDR3動作は、デバイスがリセットされ、VDDおよびVDDQがDDR3動作用に変更された場合にのみ使用できます。

^ 「DDR3Lメモリとは何ですか?」。Dell.com。デル。2016-10-03 。

^ 「JESD79-3、1.25 V DDR3U-800、DDR3U-1066、DDR3U-1333、およびDDR3U-1600の補遺No.2」。2011年10月。

^ 「仕様は、無数の家庭用電化製品、ネットワーク、およびコンピュータ製品の低消費電力を促進します」。

^ 「JESD79-3、1.25 V DDR3U-800、DDR3U-1066、DDR3U-1333、およびDDR3U-1600の補遺No.2」。

^ 「DDR3:よくある質問」(PDF)。2009年12月29日にオリジナル(PDF)からアーカイブされました。

外部リンク

JEDEC規格No.79-3(JESD79-3:DDR3 SDRAM)

DDR3SDRAM標準JESD79-3F

JESD79-3の補遺No.1-1.35V DDR3L-800、DDR3L-1066、DDR3L-1333、DDR3L-1600、およびDDR3L-1866(JESD79-3-1A.01)

JESD79-3の補遺No.2-1.25 V DDR3U-800、DDR3U-1066、DDR3U-1333、およびDDR3U-1600

JESD79-3の補遺No.3-3DスタックSDRAM

SPD(Serial Presence Detect)、JEDEC規格No. 21-C(JESD21C:ソリッドステートメモリ用のJEDEC構成)

SPD Annex K-DDR3 SDRAMモジュールのシリアルプレゼンス検出(SPD)(SPD4_01_02_11)

DDR、DDR2、DDR3メモリスロットのテスト

DDR3同期DRAMメモリ”