DDR4_SDRAM

はDDR4SDRAMについてです。グラフィックDDR4については、

GDDR4SDRAMを参照してビデオゲームについては、

Dance Dance Revolution4thMixを参照して

ダブルデータレート4同期ダイナミックランダムアクセスメモリ(DDR4 SDRAM)は、高帯域幅(「ダブルデータレート」)インターフェイスを備えた同期ダイナミックランダムアクセスメモリの一種です。 DDR4 SDRAM ダブルデータレート4同期ダイナミックランダムアクセスメモリ

RAMの種類16 iB

DDR4-2666 1.2 V UDIMM デベロッパー JEDEC タイプ

同期ダイナミックランダムアクセスメモリ(SDRAM)

世代第4世代 発売日

2014年 (2014)

基準

DDR4-1600(PC4-12800)

DDR4-1866(PC4-14900)

DDR4-2133(PC4-17000)

DDR4-2400(PC4-19200)

DDR4-2666(PC4-21333)

DDR4-2933(PC4-23466)

DDR4-3200(PC4-25600)

クロックレート

800〜1600 MHz

電圧

リファレンス1.2V

前任者

DDR3 SDRAM(2007)

後継

DDR5 SDRAM(2020)

2014年に市場にリリースされた は、ダイナミックランダムアクセスメモリ(DRAM)の変形であり、1970年代初頭から使用されているものもあり、より高速です。DDR2およびDDR3テクノロジーの後継。

DDR4は、他の要因に加えて、信号電圧と物理インターフェイスが異なるため、以前のタイプのランダムアクセスメモリ(RAM)と互換性がありません。

DDR4 SDRAMは、 ECCメモリに重点を置いて2014年第2四半期に一般市場にリリースされましたが、非ECC DDR4モジュールは、 DDR4メモリを必要とするHaswell-Eプロセッサの発売に伴い2014年第3四半期に利用可能になりました。

コンテンツ

1 特徴

2 タイムライン

2.1 市場の認識と採用

3 手術

3.1 コマンドエンコーディング 3.2 設計上の考慮事項 3.3 モジュールのパッケージ

4 モジュール

4.1 JEDEC標準DDR4モジュール

5 後継

6 も参照してください

7 ノート

8 参考文献

9 外部リンク

特徴

DDR4の前身であるDDR3に対する主な利点には、より高いモジュール密度とより低い電圧要件、およびより高いデータレート転送速度が含まれます。DDR4規格では、最大64 GBの容量のDIMMが可能ですが、DDR3ではDIMMあたり最大16GBです。

前世代のDDRメモリとは異なり、プリフェッチはDDR3で使用されている8nを超えて増加し :16 基本バーストサイズは8つの64ビットワードであり、1秒あたりにより多くの読み取り/書き込みコマンドを送信することでより高い帯域幅が実現されます。これを可能にするために、規格はDRAMバンクを2つまたは4つの選択可能なバンクグループに分割し、異なるバンクグループへの転送をより迅速に行うことができます。

消費電力は速度とともに増加するため、電圧を下げると、不当な電力や冷却を必要とせずに、より高速な動作が可能になります。

DDR4は、周波数が400〜1067 MHz(DDR3-800〜DDR3-2133)であるのに対し、周波数が800〜1600 MHz(DDR4-1600〜DDR4-3200)の1.2Vの電圧で動作します および1.5VのDDR3の電圧要件。DDRの性質上、速度は通常、これらの数値の2倍としてアドバタイズされます(DDR3-1600およびDDR4-2400が一般的であり、DDR4-3200、DDR4-4800、およびDDR4-5000は高コストで入手可能です)。DDR3の1.35V低電圧標準DDR3Lとは異なり、DDR4のDDR4L低電圧バージョンはありません。

タイムライン

最初のDDR4メモリモジュールのプロトタイプは

Samsungによって製造され、2011年1月に発表されました。

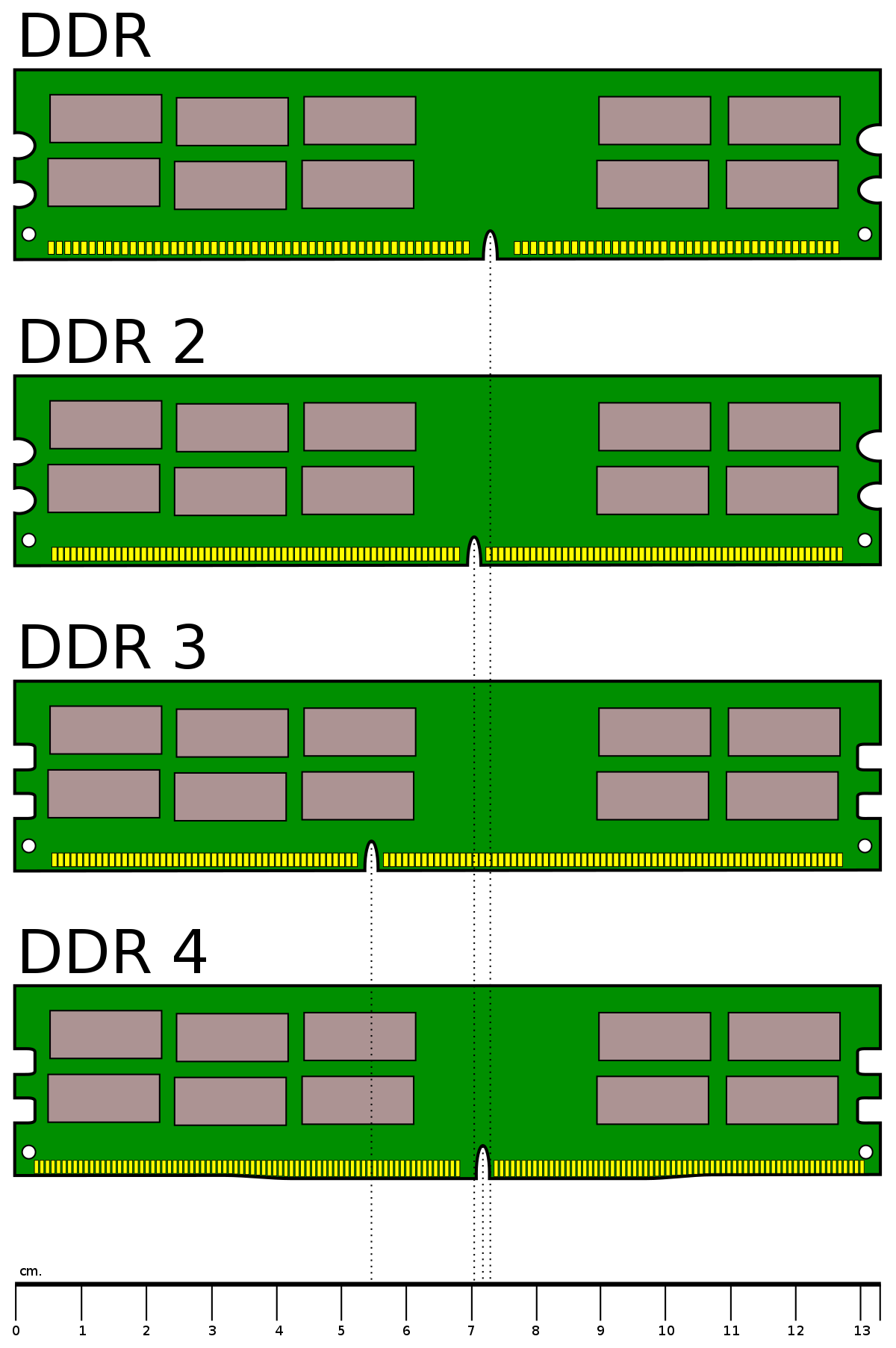

DDR、 DDR2、 DDR3、およびDDR4SDRAM

の物理的な比較

8 GB DDR4メモリモジュール

の前面と背面

2005年:標準化団体JEDECは、2007年にDDR3が発売される約2年前の2005年頃にDDR3の後継機の開発に着手しました。 DDR4の高レベルアーキテクチャは2008年に完成する予定でした。

2007年:2007年にいくつかの事前情報が公開され 、 Qimondaのゲストスピーカーが2008年8月のサンフランシスコ Intel Developer Forum(IDF)でのプレゼンテーションで詳細を公開しました。 DDR4は、1.2ボルトで30 nmのプロセスを含み、バス周波数は2133 MT / sの「通常の」速度と3200MT / sの「愛好家」の速度であり、市場に到達していると説明されました。 2012年、2013年に1ボルトに移行する前。

2009年: 2月、Samsungは40 nm DRAMチップを検証しました。これは、2009年にDRAMチップが50 nmプロセスに移行し始めたばかりであったため、DDR4開発に向けた「重要なステップ」と見なされています 。

2010:その後、東京のMemCon 2010(コンピュータメモリ業界のイベント)で詳細が明らかになり、JEDECディレクターによる「DDR4を再考する時間」というタイトルのプレゼンテーションと「新しいロードマップ:より現実的なロードマップ」というタイトルのスライドがありました。 is 2015」により、一部のWebサイトは、DDR4の導入がおそらくまたは間違いなく 2015年まで延期されたと報告しました。ただし、DDR4テストサンプルは、2011年初頭の当初のスケジュールに沿って発表されました。大規模な商業生産と市場へのリリースが2012年に予定されているとアドバイスし始めました。

2011年: 1月、Samsungは、 30〜39nmのプロセスに基づく2GB DDR4DRAMモジュールのテストの完了とリリースを発表しました。 1.2Vで2133MT / sの最大データ転送速度を持ち、 疑似オープンドレインテクノロジー(グラフィックスDDRメモリから採用)を使用し、同等のDDR3モジュールよりも消費電力が40%少なくなっています。 4月、Hynixは2 GB DDR4モジュールを2400MT / sで製造し、30〜39nmのプロセスで1.2Vで動作することを発表しました(正確なプロセスは指定されていません)。 2] 2012年下半期に大量生産を開始する予定であると付け加えます。 DDR4の半導体プロセスは、2012年後半から2014年のいずれかの時点でサブ30nmに移行すると予想されます。

2012年: 5月、Micronは、2012年後半に30nmモジュールの生産を開始することを目指していると発表しました。7月、Samsungは、エンタープライズサーバーシステム用のDDR4 SDRAMを使用して、業界初の16 GB 登録済みデュアルインラインメモリモジュール(RDIMM)のサンプリングを開始すると発表しました。 9月、JEDECはDDR4の最終仕様をリリースしました。

2013年: DDR4は2013年にDRAM市場の5%を占めると予想され 、 2015年頃にマスマーケットで採用され、50%の市場浸透率に達すると予想されていました。ただし、2013年の時点では、DDR4の採用は遅れており、2016年以降まで市場の大部分に到達することは期待されていませんでした。したがって、DDR3からDDR4への移行は、DDR3がDDR2を介したマスマーケット移行を達成するのにかかる約5年よりも長くかかります。一部、これは、他のコンポーネントに必要な変更がコンピューターシステムの他のすべての部分に影響を与えるためであり、DDR4で動作するように更新する必要が

2014年: 4月、ハイニックスは、 20nmテクノロジーを使用した8ギガビットDDR4をベースにした世界初の最高密度128GBモジュールを開発したと発表しました 。このモジュールは、64ビットI / Oで2133MHzで動作し、1秒あたり最大17GBのデータを処理します。

2016年: 4月、Samsungは、「10 nmクラス」プロセスでDRAMの大量生産を開始したことを発表しました。これは、16nmから19nmの1xnmノードレジームを意味し、30%高速なデータ転送をサポートします。 3,200 Mbit / sの速度。以前は、20nmのサイズが使用されていました。

市場の認識と採用

2013年4月、元々 IDCの一部であったアメリカの技術研究ビジネスであるInternational Data Group (IDG)のニュースライター が、DDR4SDRAMに関連する彼らの認識の分析を作成しました。結論として、低速であるが低電力のメモリを使用するモバイルコンピューティングやその他のデバイスの人気の高まり、従来のデスクトップコンピューティングセクターの成長の鈍化、およびメモリ製造市場の統合により、RAMのマージンはきつい。

その結果、新技術に必要なプレミアム価格を実現するのは難しく、容量は他のセクターにシフトしていました。SDRAMのメーカーとチップセットの作成者は、ある程度、「岩と困難な場所の間に立ち往生」しており、「 DDR4製品にプレミアムを支払うことは誰も望んでおらず、メーカーは、入手しない場合はメモリを作りたくない」と考えていました。 iSuppliのMikeHowardによると、「プレミアム」です。したがって、デスクトップコンピューティングへの消費者心理の転換と、 IntelおよびAMDによるDDR4サポートを備えたプロセッサのリリースは、「積極的な」成長につながる可能性が

Intelの2014年のHaswellロードマップは、 Haswell-EPプロセッサでのDDR4SDRAMの同社の最初の使用を明らかにしました。

2016年に発表され2017年に出荷されたAMDのRyzenプロセッサは、DDR4SDRAMを使用しています。

手術

このセクションを更新 する必要があります 。 DDR4チップは1.2V電源を使用します :16 VPPと呼ばれるワードラインブースト用の2.5V補助電源 :16 、標準の1.5VのDDR3チップと比較して低電圧2013年に登場する1.35Vのバリアント。DDR4は2133MT / sの転送速度で導入されると予想されます :18 は2013年までに潜在的な4266 MT / s に上昇すると推定されます。最小転送速度は2133です。 MT / sは、DDR3速度の進歩によるものと言われ、2133 MT / sに達する可能性があり、この速度未満でDDR4を指定することによる商業的利益はほとんどありませんでした。 Techgageは、Samsungの2011年1月のエンジニアリングサンプルを13クロックサイクルのCASレイテンシーであると解釈しました。これは、DDR2からDDR3への移行に匹敵すると説明されています。

内部バンクは16(4バンク選択ビット)に増加し、DIMMごとに最大8ランクになります。 :16

プロトコルの変更は次のとおりです。 :20

コマンド/アドレスバスのパリティ

データバス反転(GDDR4など)

データバスのCRC

オンダイターミネーションをより適切に制御できるようにする、DIMM上の個々のDRAMの独立したプログラミング。

おそらくTSV(「シリコン貫通電極」)または他の3Dスタッキングプロセスを使用して、メモリ密度の増加が予想されます。 DDR4仕様には、JEDEC によると、「最初から」標準化された3Dスタッキングが含まれ、最大8つのスタックダイが用意されています。 :12 X-bit Labsは、「結果として、非常に高密度のDDR4メモリチップは比較的安価になる」と予測しました。

スイッチドメモリバンクも、サーバーで期待されるオプションです。

2008年に、チャージポンプや電圧レギュレータなどの非スケーリングアナログ要素と追加の回路が「帯域幅の大幅な増加を可能にしましたが、ダイ領域をはるかに多く消費する」という本のWafer Level 3-D ICs ProcessTechnologyで懸念が提起されました。例としては、CRCエラー検出、オンダイターミネーション、バーストハードウェア、プログラム可能なパイプライン、低インピーダンス、センスアンプの必要性の高まり(低電圧によるビットラインあたりのビット数の減少に起因)などがその結果、メモリアレイ自体に使用されるダイの量は、SDRAMおよびDDR1の70〜78%からDDR2の47%、DDR3の38%、潜在的に30未満に減少したと著者は述べています。 DDR4の場合は%。

仕様では、2、4、8、および16 GBの容量を持つ×4、×8、および×16メモリデバイスの標準が定義されています。

コマンドエンコーディング

DDR4コマンドエンコーディング

指示 CS

BG1–0、BA1–0

活動 A17 A16 RAS A15 CAS A14 WE A13

紀元前12年A11 A10 AP

A9–0

選択解除(操作なし) HX

アクティブ(アクティブ化):行を開きます L

銀行 L 行アドレス

操作なし LV H V H H H V

ZQキャリブレーション LV H V H H L V

長いです V 読み取り(BC、バーストチョップ) L

銀行H V H L H V

紀元前V AP 桁

書き込み(AP、自動プリチャージ) L

銀行H V H L L V

紀元前V AP 桁

未割り当て、予約済み LV v V L H H V

すべての銀行にプリチャージする LV H V L H L VH V

1つのバンクをプリチャージする L

銀行H V L H L V L V 更新 LV H V L L H V

モードレジスタセット(MR0〜MR6) L

登録H L L L L L

データ

信号レベルH、高い L、低

V、低または高、有効な信号

X、無関係

論理レベル

アクティブ

非活性

通訳なし

それでも基本的に同じように動作しますが、DDR4は前のSDRAM世代で使用されていたコマンドフォーマットに1つの大きな変更を加えます。新しいコマンド信号ACTは、アクティブ化(行を開く)コマンドを示すためにローになっています。

activateコマンドは他のどのアドレスビットよりも多くのアドレスビットを必要とするため(16ギガビット部分に18行のアドレスビット)、標準のRAS、CAS、およびWE アクティブロー信号は、 ACTがハイのときに使用されない上位アドレスビットと共有されます。。以前にアクティブ化コマンドをエンコードしたRAS = LとCAS = WE = Hの組み合わせは使用されません。

以前のSDRAMエンコーディングと同様に、A10を使用してコマンドバリアントを選択します。読み取りおよび書き込みコマンドで自動プリチャージし、プリチャージコマンドで1つのバンクとすべてのバンクを比較します。また、ZQキャリブレーションコマンドの2つのバリエーションを選択します。

DDR3と同様に、A12はバーストチョップを要求するために使用されます。4回の転送後の8回の転送バーストの切り捨てです。バンクはまだビジーで、8つの転送時間が経過するまで他のコマンドを使用できませんが、別のバンクにアクセスできます。

また、銀行の住所が大幅に増えました。各DRAM内で最大16個のバンクを選択するための4つのバンク選択ビットが2つのバンクアドレスビット(BA0、BA1)と2つのバンクグループビット(BG0、BG1)です。同じ銀行グループ内の銀行にアクセスする場合、追加のタイミング制限が別の銀行グループの銀行にアクセスする方が高速です。

さらに、3つのチップセレクト信号(C0、C1、C2)があり、最大8つのスタックチップを単一のDRAMパッケージ内に配置できます。これらは事実上、さらに3つのバンク選択ビットとして機能し、合計で7つ(128の可能なバンク)になります。

標準の

転送速度は1600、1866、2133、2400、2666、2933 、

および3200 MT / s (12⁄15、14⁄15、16⁄15、18⁄15、20⁄15、22⁄ _ _ _ _ _ 15、および

24⁄15 GHzクロック周波数、ダブルデータレート)、最大DDR4-4800 (2400 MHzクロック)の速度が市販されています。

設計上の考慮事項

Micron TechnologyのDDR4チームは、ICおよびPCB設計のいくつかの重要なポイントを特定しました。

IC設計:

VrefDQキャリブレーション(DDR4「VrefDQキャリブレーションはコントローラーによって実行される必要があります」);

新しいアドレス指定スキーム(「バンクグループ化」、RAS、CAS、およびWEコマンドを置き換えるACT、エラーチェック用のPARおよびAlert、データバス反転用のDBI )。

新しい省電力機能(低電力自動セルフリフレッシュ、温度制御リフレッシュ、細粒度リフレッシュ、データバス反転、およびCMD / ADDR遅延)。

回路基板の設計:

新しい電源(1.2VでのVDD / VDDQおよび2.5VでのVPPとして知られるワードラインブースト);

VrefDQはDRAMの内部に供給され、VrefCAはボードの外部に供給される必要が

DQピンは、疑似オープンドレインI / Oを使用してHighで終端します(これは、VTTにセンタータップされているDDR3のCAピンとは異なります)。

Rowhammer緩和技術には、より大きなストレージコンデンサ、アドレス空間レイアウトのランダム化を使用するようにアドレスラインを変更すること、および高速の書き込み/読み取り速度で不安定になる可能性のある潜在的な境界条件をさらに分離するデュアル電圧I / Oラインが含まれます。

モジュールのパッケージ

Micron製の16GB

DDR4SO-DIMMモジュール

DDR4メモリは、240ピンDDR3 DIMMと同じサイズの288ピンデュアルインラインメモリモジュール(DIMM)で提供されます。同じ5¼インチ(133.35 mm)の標準DIMM長さ内に増加した数に合うようにピンの間隔を狭くします(1.0ではなく0.85 mm

)が、高さはわずかに増加します(30.35 mm /1.2インチではなく31.25mm / 1.23インチ) )信号のルーティングを容易にし、より多くの信号層に対応するために厚さも増加します(1.0から1.2 mmに)。 DDR4 DIMMモジュールにはわずかに湾曲したエッジコネクタがあるため、モジュールの挿入中にすべてのピンが同時にかみ合うわけではなく、挿入力が低下します。

DDR4 SO-DIMMには、DDR3 SO-DIMMの204ピンの代わりに260ピンがあり、0.6 mmではなく0.5の間隔で、2.0 mm幅(69.6mm対67.6mm)ですが、高さは同じ30mmのままです。

Intelは、Skylakeマイクロアーキテクチャ用に、 UniDIMMという名前のSO-DIMMパッケージを設計しました。このパッケージには、DDR3またはDDR4チップを搭載できます。同時に、Skylake CPUの統合メモリコントローラー(IMC)は、どちらのタイプのメモリでも動作できることが発表されています。UniDIMMの目的は、DDR3からDDR4への市場移行を支援することです。この場合、価格設定と可用性により、RAMタイプの切り替えが望ましくない場合がUniDIMMの寸法とピン数は通常のDDR4SO-DIMMと同じですが、互換性のないDDR4 SO-DIMMソケットで誤って使用されないように、エッジコネクタのノッチの配置が異なります。

モジュール

JEDEC標準DDR4モジュール

標準名

メモリクロック(MHz) I / Oバスクロック(MHz) データレート(MT / s) モジュール名

ピーク転送速度(MB /秒) タイミングCL-tRCD-tRP CASレイテンシ(ns)

DDR4-1600J * DDR4-1600K DDR4-1600L200 800 1600PC4-12800 12800

10-10-10 11-11-11 12-12-12

12.5 13.75 15

DDR4-1866L * DDR4-1866M DDR4-1866N233.33 933.33 1866.67 PC4-14900 14933.33

12-12-12 13-13-13 14-14-14

12.857 13.929 15

DDR4-2133N * DDR4-2133P DDR4-2133R266.67 1066.67 2133.33 PC4-17000 17066.67

14-14-14 15-15-15 16-16-16

13.125 14.063 15

DDR4-2400P * DDR4-2400R DDR4-2400T DDR4-2400U300 1200 2400PC4-19200 19200

15-15-15 16-16-16 17-17-17 18-18-18

12.5 13.32 14.16 15

DDR4-2666T DDR4-2666U DDR4-2666V DDR4-2666W333.33 1333.33 2666.67 PC4-21300 21333.33

17-17-17 18-18-18 19-19-19 20-20-20

12.75 13.50 14.25 15

DDR4-2933V DDR4-2933W DDR4-2933Y DDR4-2933AA366.67 1466.67 2933.33 PC4-23466 23466.67

19-19-19 20-20-20 21-21-21 22-22-22

12.96 13.64 14.32 15

DDR4-3200W DDR4-3200AA DDR4-3200AC400 1600 3200PC4-25600 25600

20-20-20 22-22-22 24-24-24

12.5 13.75 15

CASレイテンシー(CL)

列アドレスをメモリに送信してから、それに応じてデータを開始するまでの

クロックサイクル tRCD 行のアクティブ化と読み取り/書き込みの間のクロックサイクル tRP 行のプリチャージとアクティブ化の間のクロックサイクル

DDR4-xxxxはビットごとのデータ転送速度を示し、通常はDDRチップを表すために使用されます。PC4-xxxxxは、全体の転送速度をメガバイト/秒で示し、モジュール(組み立てられたDIMM)にのみ適用されます。DDR4メモリモジュールは8バイト(64データビット)幅のバスでデータを転送するため、モジュールのピーク転送速度は、1秒あたりの転送数に8を掛けて計算されます。

後継

2016 Intel Developer Forumで、 DDR5SDRAMの将来について議論されました。仕様は2016年末に最終決定されましたが、2020年までに利用できるモジュールはありません。 DDR4の置き換えを目的とした他のメモリテクノロジ(バージョン3および4のHBM ) も提案されています。

2011年、JEDECはWide I / O2規格を公開しました。複数のメモリダイをスタックしますが、CPUの真上で同じパッケージ内でそれを行います。このメモリレイアウトは、DDR4 SDRAMよりも高い帯域幅と優れた電力性能を提供し、短い信号長で広いインターフェイスを可能にします。これは主に、スマートフォンなどの高性能組み込みおよびモバイルデバイスで使用されるさまざまなモバイルDDR XSDRAM規格を置き換えることを目的としています。 Hynixは、JEDEC JESD235として公開された同様の高帯域幅メモリ(HBM)を提案しました。Wide I / O 2とHBMはどちらも、非常にワイドなパラレルメモリインターフェイスを使用します。WideI/ O 2の場合は最大512ビット幅(DDR4の場合は64ビット)で、DDR4よりも低い周波数で動作します。ワイドI / O 2は、スマートフォンなどの高性能コンパクトデバイスを対象としており、プロセッサまたはシステムオンチップ(SoC)パッケージに統合されます。HBMはグラフィックメモリと一般的なコンピューティングを対象としていますが、HMCはハイエンドサーバーとエンタープライズアプリケーションを対象としています。

Micron Technologyのハイブリッドメモリキューブ(HMC)スタックメモリは、シリアルインターフェイスを使用します。他の多くのコンピュータバスは、パラレルバスをシリアルバスに置き換える方向に移行しています。たとえば、シリアルATAがパラレルATAに置き換わり、PCI ExpressがPCIに置き換わり、シリアルポートがパラレルポートに置き換わっています。一般に、シリアルバスはスケールアップが容易で、ワイヤ/トレースが少ないため、シリアルバスを使用する回路基板の設計が容易になります。

長期的には、専門家は、PCM(相変化メモリ)、RRAM(抵抗変化型メモリ)、 MRAM(磁気抵抗性ランダムアクセスメモリ)などの不揮発性RAMタイプがDDR4SDRAMとその後継メモリに取って代わる可能性があると推測しています。

GDDR5 SGRAMは、 DDR4の前に導入されたDDR3 同期グラフィックスRAMのグラフィックスタイプであり、DDR4の後継ではありません。

も参照してください

![]()

テクノロジーポータル

同期ダイナミックランダムアクセスメモリ –DDRメモリタイプの主な記事

デバイス帯域幅のリスト

メモリのタイミング

ノート

^ 一部の工場でオーバークロックされたDDR3メモリモジュールは、最大1600MHzのより高い周波数で動作します。

^ プロトタイプとして、このDDR4メモリモジュールの下部にはフラットエッジコネクタがありますが、製品版DDR4 DIMMモジュールにはわずかに湾曲したエッジコネクタがあるため、モジュールの挿入時にすべてのピンが同時にかみ合うわけではなく、挿入力が低下します。

^ 1 MT = 100万回の転送 ^ 1 MB = 100万バイト

参考文献

^ g h ここで、K、M、G、またはTは、1024の累乗に基づくバイナリプレフィックスを指します。

^ Marc(2011-04-05)。「Hynixは最初のDDR4モジュールを製造しています」。ハードウェアであること。2012年4月15日にオリジナルからアーカイブされました。

^ Micron が動作中のDDR4RAMをからかう、Engadget、2012-05-08 、取得済み2012-05-08

^ 「SamsungはDDR4を大量生産します」。

^ DRAMストーリー(PDF)、IEEE、2008年、p。10 、取得2012-01-23

^ 「重要なDDR4サーバーメモリが利用可能になりました」。グローブニュースワイヤー。2014年6月2日。

^ btarunr(2014年9月14日)。「インテルが主流のDDR3とDDR4の間でどのように移行する予定か」。TechPowerUp 。

^ Wang、David(2013年3月12日)。「なぜDDR4に移行するのですか?」。Inphi Corp. – EETimes経由。

^ g Jung、JY(2012-09-11)、「DRAMの進歩がサーバーインフラストラクチャに与える影響」、Intel Developer Forum 2012、Intel、Samsung; 2012年11月27日にオリジナルからアーカイブされ、されたアクティブなイベント

^ 「メインメモリ:DDR4&DDR5SDRAM」。JEDEC 。

^ 「DDR3SDRAM標準JESD79-3F、秒。表69 –スピードビン別のタイミングパラメータ」。JEDEC。2012年7月。

^ 「VengeanceLPメモリ— 8GB 1600MHz CL9 DDR3(CML8GX3M1A1600C9)」。Corsair 。

^ 「DDR4– DDR3からの移行の利点」、製品、2014年8月20日取得 ^ 「Corsairは世界最速のDDR4RAMを解き放ち、16GBのコストはゲーミングPCよりも高くなります(おそらく)| TechRadar」。www.techradar.com。

^ “”Molex DDR4 DIMMソケット、ハロゲンフリー””。アローヨーロッパ。モレックス。2012 。

^ Sobolev、Vyacheslav(2005-05-31)。「JEDEC:途中のメモリ規格」。Digitimes。技術経由。2013年12月3日にオリジナルからアーカイブされました。DDR3を超えるメモリテクノロジに関する初期調査はすでに開始されています。JEDECには、標準化プロセスのさまざまな段階(現在の世代、次世代、および将来)に常に約3世代のメモリが

^ 「DDR3:よくある質問」(PDF)。キングストンテクノロジー。2011年7月28日にオリジナル(PDF)からアーカイブされました。2007年6月に発売されたDDR3メモリ

^ Valich、Theo(2007-05-02)。「5月9日のDDR3ローンチセット」。インクワイアラー。2010年2月5日にオリジナルからアーカイブされました。

CS1 maint:不適切なURL(リンク)

^ ハマーシュミット、クリストフ(2007-08-29)。「不揮発性メモリはJEDEC会議の秘密のスターです」。EETimes 。

^ “”DDR4 –DDR3メモリの後継””。「H」(オンライン版)。2008-08-21。2011年5月26日にオリジナルからアーカイブされました。JEDEC標準化委員会は約1年前に同様の数字を引用しました

^ グラハム・スミス、ダリエン(2008-08-19)。「IDF:DDR3は2009年中にDDR2に追いつきません」。PCPro。2011年6月7日にオリジナルからアーカイブされました。

^ Volker、Rißka(2008-08-21)。「IDF:DDR4 als Hauptspeicher ab2012」 [IntelDeveloperForum:2012年のメインメモリとしてのDDR4]。Computerbase(ドイツ語)。DE 。(英語)

^ Novakovic、Nebojsa(2008-08-19)。「キマンダ:DDR3が前進しています」。インクワイアラー。2010年11月25日にオリジナルからアーカイブされました。

CS1 maint:不適切なURL(リンク)

^ Gruener、Wolfgang(2009年2月4日)。「Samsungは最初に検証された40nmDRAMを使用したDDR4へのヒント」。毎日TG。2009年5月24日にオリジナルからアーカイブされました。

^ Jansen、Ng(2009年1月20日)。「DDR3は2009年に安く、速くなります」。デイリーテック。2009年6月22日にオリジナルからアーカイブされました。

^ Gervasi、ビル。「DDR4を再考する時」(PDF)。2010年7月。DiscobolusDesigns 。

^ 「DDR4-Speicherkommtwohlspäteralsbishergeplant」 [DDR4メモリはおそらく以前の計画よりも遅い]。ハイゼ(ドイツ語)。DE。2010-08-17 。(英語)

^ Nilsson、Lars-Göran(2010-08-16)。「DDR4は2015年まで期待されていません」。半正確。

^ 全滅者(2010-08-18)。「WorksのDDR4メモリは4.266GHzに達します」。WCCFtech 。

^ 「サムスンは30nmクラスの技術を使用して、業界初のDDR4DRAMを開発しました」。サムスン。2011-04-11 。

^ ペリー、ライアン(2011-01-06)。「サムスンは最初の30nmDDR4DRAMを開発しました」。テックゲージ。

^ 「Samsungは30nmクラスの技術を使用して業界初のDDR4DRAMを開発しました」(プレスリリース)。サムスン。2011-01-04 。

^ Protalinski、Emil(2011-01-04)、SamsungはDDR4メモリを開発し、最大40%効率が向上、Techspot 、 2012-01-23を取得

^ 後藤、弘茂。「MEM4Gbps時代へ」と「次世代4GbpsDDR4メモリに向けて」。2010年8月16日。JP:PCウォッチ。(英訳)

^ 「図:予想されるDDR4タイムライン」。2010-08-16。JP:PCウォッチ。

^ 「SamsungSamples業界初のサーバー用DDR4メモリモジュール」(プレスリリース)。サムスン。2013年11月4日にオリジナルからアーカイブされました。

^ 「SamsungSamples業界初のDDR4メモリテクノロジーに基づく16ギガバイトサーバーモジュール」(プレスリリース)。サムスン。

^ Emily Desjardins(2012年9月25日)。「JEDECがDDR4規格の公開を発表」。JEDEC 。

^ Shah、Agam(2013年4月12日)、「DDR4メモリの採用は遅延に直面」、TechHive、IDG 、 2013年6月30日取得 ^ Shilov、Anton(2010-08-16)、4.266 GHzに到達する次世代DDR4メモリ、Xbitラボ、 2010-12-19にオリジナルからアーカイブ、2011-01-03を取得

^ 1メガビット= 100万ビット

^ 「サムスンは10ナノメートルクラスのDRAMの生産を開始します」。公式DDR4メモリテクノロジーニュースブログ。2016-05-21 。

^ 「1xnmDRAMの課題」。半導体工学。2016-02-18 。

^ Shah、Agam(2013-04-12)。「DDR4メモリの採用は遅れに直面しています」。IDGニュース。

^ 「Haswell-E–インテル初の8コアデスクトッププロセッサが公開されました」。TechPowerUp。

^ 「最大32コア、8チャネルDDR4を搭載するAMDのZenプロセッサ」。

^ DDR4を楽しみにしています、英国:PC pro、2008-08-19、2012-01-23を取得

^ IDF:DDR4 – DDR3メモリの後継(オンライン版)、英国:Heise、2008年8月21日、2012年1月23日取得

^ スウィンバーン、リチャード(2010-08-26)。「DDR4:期待できること」。ビットテック。 ページ1、2、3。_ _ _

^ 「JEDECが3D-IC規格開発の幅広いスペクトルを発表」(プレスリリース)。JEDEC。2011-03-17 。

^ タン、グットマン; タン、レイフ(2008)。ウェーハレベル3-DICプロセス技術。スプリンガー。p。278(セクション12.3.4–12.3.5)。ISBN

978-0-38776534-1。

^ JESD79-4 –JEDEC標準DDR4SDRAM 2012年9月(PDF)、X開発者 。

^ JEDEC標準JESD79-4:DDR4 SDRAM、JEDEC Solid State Technology Association、2012年9月、2012年10月11日取得

。ユーザー名「cypherpunks」とパスワード「cypherpunks」でダウンロードできます。

^ JEDEC標準JESD79-4B:DDR4 SDRAM(PDF)、JEDEC Solid State Technology Association、2017年6月、2017年8月18日取得 。ユーザー名「cypherpunks」とパスワード「cypherpunks」でダウンロードできます。

^ リンチ、スティーブン(2017年6月19日)。「G.Skillはその驚異的な高速DDR4-4800をComputexにもたらしました」。トムスハードウェア。

^ “”DDR4 DRAMの最新のスクープが必要ですか?IC、システム、およびPCBの設計者が関心を持っているMicronチームからの技術的な回答がいくつかあります””。デナリメモリレポート、メモリ市場レポートサイト。2012-07-26。2013年12月2日にオリジナルからアーカイブされました。

^ MO-309E(PDF)(ホワイトペーパー)、JEDEC 、 2014年8月20日取得 。

^ 「DDR4SDRAMSO-DIMM(MTA18ASF1G72HZ、8 GB)データセット」(PDF)。マイクロンテクノロジー。2014-09-10。2014年11月29日にオリジナル(PDF)からアーカイブされました。

^ 「インテルが主流のDDR3とDDR4の間でどのように移行する予定か」。テックパワーアップ。

^ Denneman、Frank(2015-02-25)。「メモリディープダイブ:DDR4メモリ」。frankdenneman.nl 。

^ “”Arbeitsspeicher:DDR5nähertsichlangsamderMarktreife””。Golem.de。

^ Rißka、Volker。”” “” DDR is over “”:HBM3 /HBM4bringtBandbreitefürHigh-End-Systeme””。ComputerBase。

^ ベイリー、ブライアン。「WideI / Oはゲームチェンジャーですか?」。EDN。

^ 「JEDECはワイドI / OモバイルDRAMの画期的な標準を公開しています」。Jedec。

^ “DDR4を超えて:ワイドI / O、HBM、およびハイブリッドメモリキューブの違い”。エクストリームテック。

^ 「ザイリンクス株式会社–さようならDDR、こんにちはシリアルメモリ」。ネット上のEPDT。

^ シュミッツ、タマラ(2014年10月27日)。「シリアルメモリの台頭とDDRの未来」(PDF)。

^ 「バイバイDDRnプロトコル?」。SemiWiki。

^ 「DDR5メモリが2020年にコンピュータに到達する予定であるため、DRAMは存続します」。

外部リンク

メインメモリ:DDR3&DDR4 SDRAM、JEDEC、DDR4 SDRAM標準(JESD79-4)

DDR4 (PDF) (ホワイトペーパー)、Corsair Components 、2014年10月10日にオリジナル (PDF)からアーカイブ。”