DDR_SDRAM

はDDRSDRAMについてです。グラフィックDDRについては、

GDDRを参照して

ダブルデータレート同期ダイナミックランダムアクセスメモリ(DDR SDRAM)は、コンピュータで使用されるメモリ集積回路のダブルデータレート(DDR)同期ダイナミックランダムアクセスメモリ(SDRAM)クラスです。DDR SDRAMは、遡及的にDDR1 SDRAMとも呼ばれ、 DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、およびDDR5SDRAMに取って代わられました。後継機種はいずれもDDR1SDRAMとの下位互換性がありません。つまり、DDR2、DDR3、DDR4、およびDDR5メモリモジュールは、DDR1を搭載したマザーボードでは機能しません。、 およびその逆。 DDR SDRAM ダブルデータレート同期ダイナミックランダムアクセスメモリ

デスクトップPC(DIMM)用のDDRモジュールの比較。

デスクトップPC(DIMM)用の1GB DDR-400RAMモジュールの前面と背面

デベロッパー

サムスン JEDEC

タイプ

同期ダイナミックランダムアクセスメモリ

世代DDR2 DR3 DR4 DR5

発売日

DDR: 1998

DDR2: 2003

DDR3: 2007

DDR4: 2014

DDR5: 2020 仕様 電圧

DDR: 2.5 / 2.6

DDR2: 1.8

DDR3: 1.5 / 1.35

DDR4: 1.2 / 1.05

シングルデータレート(SDR)SDRAMと比較して、DDR SDRAMインターフェイスは、電気データとクロック信号のタイミングをより厳密に制御することにより、より高い転送レートを可能にします。実装では、必要なタイミング精度に到達するために、フェーズロックループやセルフキャリブレーションなどのスキームを使用する必要が インターフェースは、ダブルポンピング(クロック信号の立ち上がりエッジと立ち下がりエッジの両方でデータを転送する)を使用して、対応するクロック周波数の増加なしにデータバス帯域幅を2倍にします。クロック周波数を低く抑えることの利点の1つは、メモリをコントローラに接続する回路基板のシグナルインテグリティ要件を軽減することです。「ダブルデータレート」という名前は、特定のクロック周波数のDDR SDRAMが、このダブルポンピングにより、同じクロック周波数で動作するSDRSDRAMのほぼ2倍の帯域幅を実現することを意味します。

データが一度に64ビット転送される場合、DDR SDRAMは、(メモリバスクロックレート)×2(デュアルレートの場合)×64(転送されるビット数)/ 8(ビット数)の転送レート(バイト/秒)を提供します。 /バイト)。したがって、バス周波数が100 MHzの場合、DDRSDRAMは 1600MB / sの最大転送速度を提供します。

コンテンツ

1 歴史

2 仕様

2.1 モジュール 2.2 チップ特性

2.2.1 ダブルデータレート(DDR)SDRAM仕様

2.3 組織

3 世代

3.1 モバイルDDR

4 も参照してください

5 参考文献

6 外部リンク

歴史

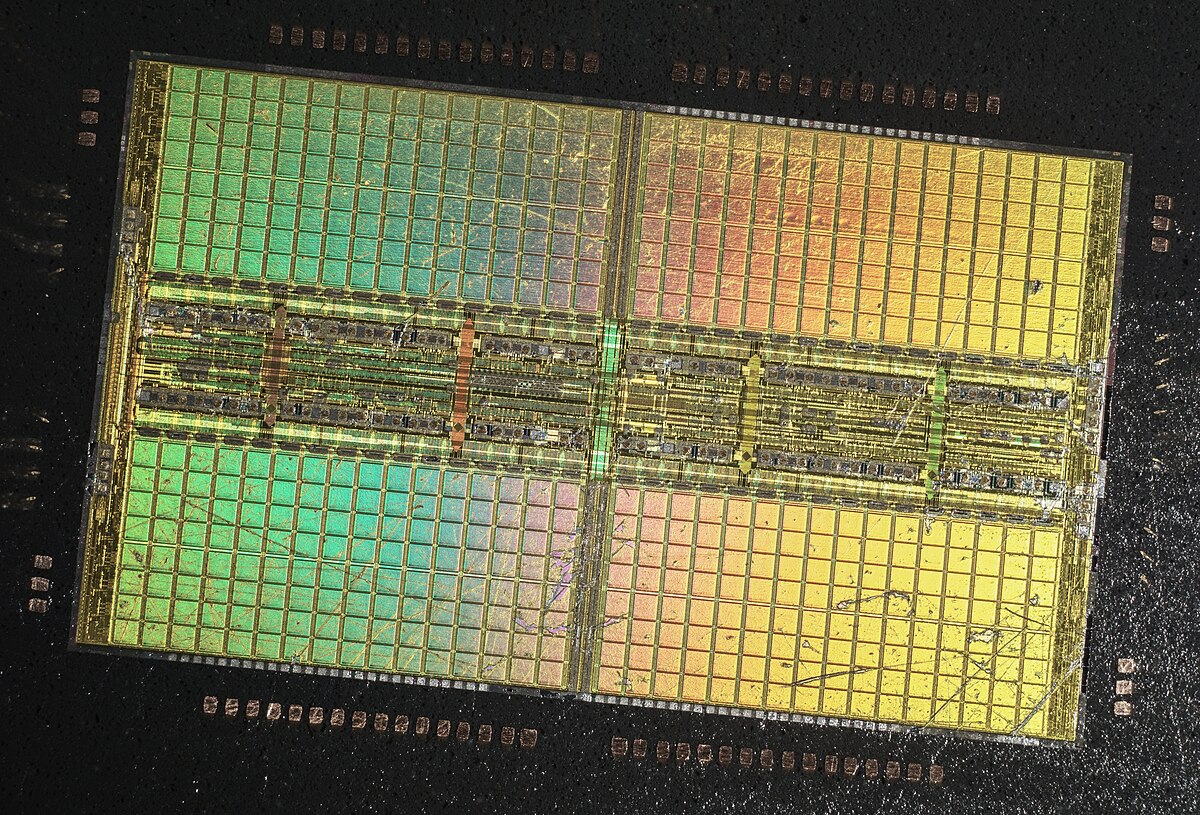

サムスンDDRSDRAM64MBitチップ

1980年代後半、IBMはデュアルエッジクロッキング機能を使用してDRAMを構築し、その結果を1990年の国際ソリッドステート回路コンベンションで発表しました。

サムスンは1997年に最初のDDRメモリプロトタイプを実証し 、 1998年6月に最初の商用DDR SDRAMチップ(64 Mb )をリリースし 、その直後に現代エレクトロニクス(現在のSKハイニックス)がリリースしました。同じ年。 DDRの開発は1996年に始まり、その仕様は2000年6月にJEDECによって最終決定されました(JESD79)。 JEDECは、DDRSDRAMのデータレートの基準を2つの部分に分けて設定しています。最初の仕様はメモリチップ用で、2番目の仕様はメモリモジュール用です。DDRSDRAMを使用した最初の小売用PCマザーボードは2000年8月にリリースされました。

仕様

単一の汎用DDRメモリモジュール

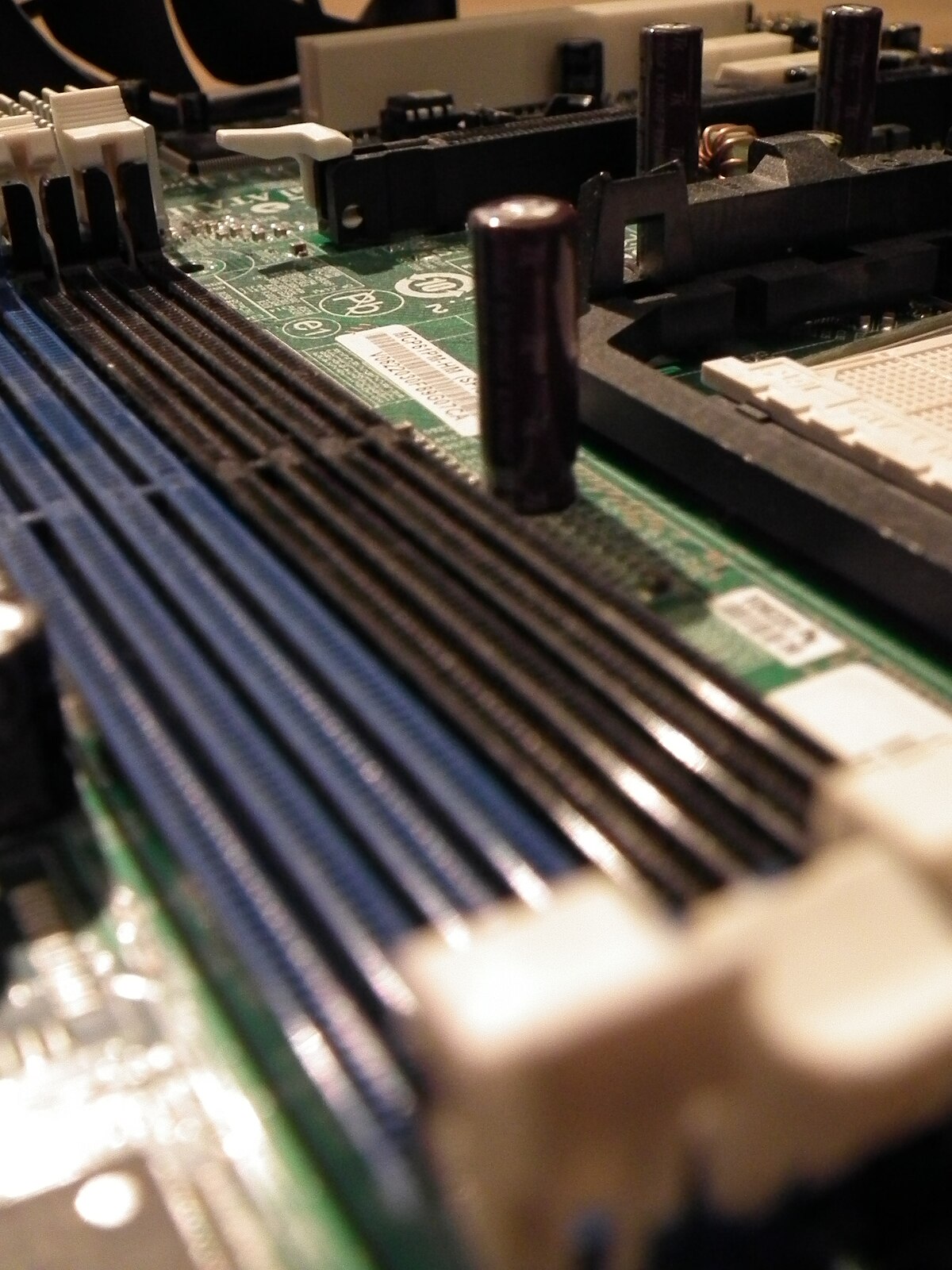

4つのDDRRAMスロット

ヒートスプレッダを備えたCorsairDDR-400メモリ

物理DDRレイアウト

ポータブル/モバイルPC( SO-DIMM)のメモリモジュールの比較。

モジュール

メモリ容量と帯域幅を増やすために、チップはモジュール上で結合されます。たとえば、DIMM用の64ビットデータバスには、並列にアドレス指定された8つの8ビットチップが必要です。共通のアドレスラインを持つ複数のチップは、メモリランクと呼ばれます。この用語は、チップの内部行およびバンクとの混同を避けるために導入されました。メモリモジュールは複数のランクを持つ場合がモジュール上のチップの物理的な配置を誤って示唆しているため、側面という用語も混乱を招きます。すべてのランクは同じメモリバス(アドレス+データ)に接続されています。チップセレクト信号は、特定のランクにコマンドを発行するために使用されます。

単一のメモリバスにモジュールを追加すると、そのドライバに追加の電気的負荷が発生します。結果として生じるバス信号速度の低下を軽減し、メモリのボトルネックを克服するために、新しいチップセットはマルチチャネルアーキテクチャを採用しています。

DDRSDRAM規格の比較

名前 チップ バス タイミング 電圧 (V)

標準 タイプ モジュール クロックレート (MHz) サイクルタイム(ns)

クロックレート(MHz) 転送速度 (MT / s) 帯域幅 (MB /秒) CL-T RCD -T RP

CASレイテンシ (ns)

DDR-200 PC-1600 100 10 100 200 1600

2.5±0.2

DDR-266 PC-2100 133⅓ 7.5 133⅓ 266.67 2133⅓ 2.5-3-3

DDR-333 PC-2700 166⅔ 6 166⅔ 333⅓ 2666⅔ 2.5 DDR-400 A PC-3200 200 5 200 400 3200 2.5-3-3 3 2.6±0.1

B 3-3-3 2.5

C 3-4-4 2

注:上記のすべては、JEDECによってJESD79Fとして指定されています。これらのリストされた仕様の間またはそれ以上のすべてのRAMデータレートは、JEDECによって標準化され多くの場合、これらは、より厳しい公差または過電圧チップを使用した単なるメーカーの最適化です。DDRSDRAMが製造されるパッケージサイズもJEDECによって標準化されています。

DDRSDRAMモジュール間にアーキテクチャ上の違いはありません。代わりに、モジュールはさまざまなクロック周波数で動作するように設計されています。たとえば、PC-1600モジュールは100 MHzで動作するように設計されており、PC-2100は133MHzで動作するように設計されています。モジュールのクロック速度は、実行が保証されているデータレートを指定するため、モジュールが作成されたクロックレートよりも低い(アンダークロック)クロックレートで実行されることが保証され、場合によっては高い(オーバークロック)クロックレートで実行される可能性が

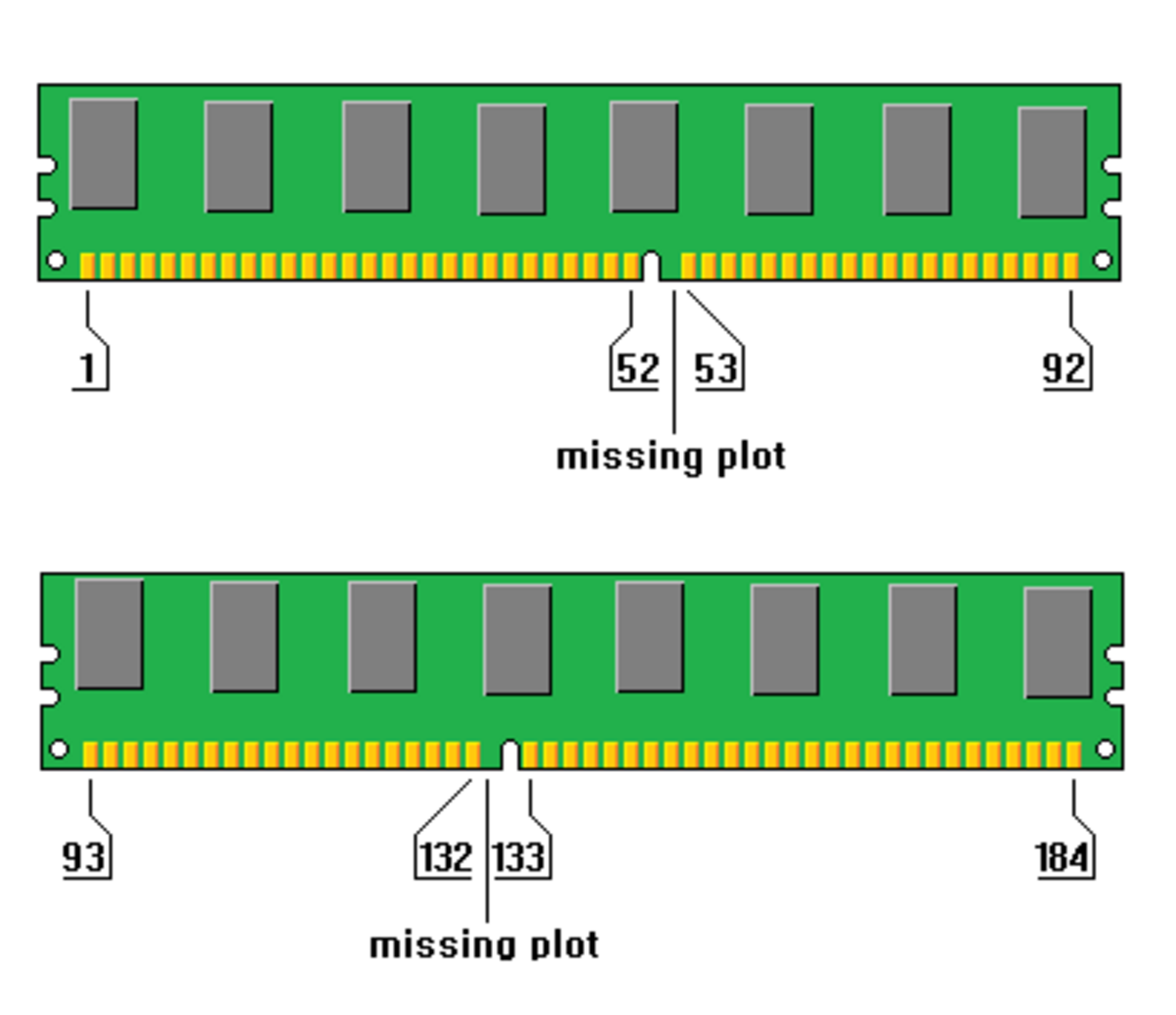

デスクトップコンピュータ用のDDRSDRAMモジュール、デュアルインラインメモリモジュール(DIMM)は、184ピン(SDRAMの168ピン、またはDDR2 SDRAMの240ピンとは対照的)を備えており、ノッチの数によってSDRAM DIMMと区別できます( DDR SDRAMには1つ、SDRAMには2つあります)。ノートブックコンピュータ用のDDRSDRAM、SO-DIMMには200ピンがあり、これはDDR2SO-DIMMと同じピン数です。これらの2つの仕様は非常によく似たノッチが付けられており、正しい一致が不明な場合は挿入時に注意する必要がほとんどのDDRSDRAMは、SDRAMの3.3 Vと比較して、2.5Vの電圧で動作します。これにより、消費電力を大幅に削減できます。DDR-400 / PC-3200規格のチップとモジュールの公称電圧は、2.6Vです。

JEDEC規格No.21–Cは、中心線に対するキーノッチの位置によって識別される、184ピンDDRの3つの可能な動作電圧を定義しています。4.5.10-7ページでは、2.5V(左)、1.8V(中央)、TBD(右)を定義しています。4.20.5–40ページでは、右のノッチ位置に3.3Vを指定しています。キーノッチ位置を決定するためのモジュールの向きは、左側に52の接触位置、右側に40の接触位置です。

動作電圧をわずかに上げると、最大速度が上がる可能性がありますが、消費電力と加熱が大きくなり、誤動作や損傷のリスクが

容量

DRAMデバイスの数

チップの数は、非

ECCモジュールの場合は8の倍数、ECCモジュールの場合は9の倍数です。チップ

は、モジュールの片面(片面)または両面( 両面)を占める可能性がDDRモジュールあたりのチップの最大数は、ECCの場合は36(9×4)、非ECCの場合は32(8×4)です。

ECCと非ECC

エラー訂正コード

を持つモジュールには

、 ECCというラベルが付けられていエラー訂正コードのないモジュールには、

非ECCのラベルが付けられます。

タイミング

CASレイテンシ(CL)、クロックサイクル時間(t

CK)、行サイクル時間(t

RC)、更新行サイクル時間(t

RFC)、行アクティブ時間(t

RAS)。

バッファリング

登録済み(またはバッファリング済み)と

バッファリングなし。 包装 通常

、 DIMMまたは

SO-DIMM。

消費電力

2005年にDDRおよびDDR2RAMを使用したテストでは、平均消費電力は

512 MBモジュールあたり1〜3Wのオーダーであるように見えました。これは、クロックレートとともに、アイドリングではなく使用時に増加します。

メーカーは、さまざまなタイプのRAMで使用される電力を推定するための計算機を作成しました。

モジュールとチップの特性は本質的に関連しています。

モジュールの総容量は、1つのチップの容量とチップの数の積です。ECCモジュールは、エラー訂正に1バイトあたり1ビット(8ビット)を使用するため、これに8/9を掛けます。したがって、特定のサイズのモジュールは、32個の小さなチップ(ECCメモリの場合は36個)、または16個(18)または8個(9)個の大きなチップから組み立てることができます。

チャネルあたりのDDRメモリバス幅は64ビット(ECCメモリの場合は72)です。モジュールの合計ビット幅は、チップあたりのビット数とチップ数の積です。また、ランク(行)の数にDDRメモリバス幅を掛けたものにも等しくなります。その結果、チップ数が多いモジュールや、×4ではなく×8チップを使用しているモジュールのランクが高くなります。

例:ECCを備えた1 GBPC2100登録DDRSDRAMモジュールのバリエーション

モジュールサイズ(GB) チップ数 チップサイズ(Mbit) チップ構成 ランク数

1 36 256 64M×4 2

1 18 512 64M×8 2

1 18 512 128M×4 1

この例では、一般的なサイズが1GBのさまざまな実世界のサーバーメモリモジュールを比較します。1 GBのメモリモジュールの購入には注意が必要です。これらのバリエーションはすべて、シングルランクまたはデュアルランクのいずれであるかを明記せずに、1つの価格帯で販売できるためです。

モジュールランクの数はサイドの数に等しいという一般的な信念が上記のデータが示すように、これは真実ではありません。2サイド/ 1ランクのモジュールも片面×8に16(18)個のチップを搭載した片面/ 2ランクのメモリモジュールも考えられますが、そのようなモジュールが製造された可能性はほとんどありません。

チップ特性

サムスンDDR-SDRAM64MBitパッケージ ダイ

DRAM密度

チップのサイズは

メガビットで測定されます。ほとんどのマザーボードは、 64M×8チップ(低密度)が含まれている場合、1GBのモジュールのみを認識します

。128M×4(高密度)の1 GBモジュールを使用すると、ほとんどの場合

機能しません。JEDEC規格では、サーバー専用に設計された登録済みモジュールに対してのみ128M×4が許可れていますが、一部の汎用メーカーは準拠していません 。 組織 64M×4 のような表記

は、メモリマトリックスに6400万(バンクx 行x 列の積)の4ビットストレージロケーションがあることを意味します。×4、×8、および

×16のDDRチップがあり×4チップを使用すると

、サーバー環境でChipkill、

メモリスクラビング、Intel SDDCなどの高度なエラー訂正機能を使用できますが、 × 8および

×16チップはやや安価です。

x8チップは主にデスクトップ/ノートブックで使用されていますが、サーバー市場に参入しています。通常は4つのバンクがあり、各バンクでアクティブにできるのは1つの行のみです。

ダブルデータレート(DDR)SDRAM仕様

Ballot JCB-99-70から、DRAMパラメトリックに関する委員会JC-42.3の承認の下で策定された、他の多数のBoardBallotによって変更されました。

標準No.79改訂ログ:

リリース1、2000年6月

リリース2、2002年5月

リリースC、2003年3月–JEDEC規格No.79C。

「この包括的な規格は、機能、機能、ACおよびDCパラメトリック、パッケージ、ピン割り当てなど、X4 / X8 / X16データインターフェイスを備えた64Mbから1GbDDR SDRAMに必要なすべての側面を定義しています。この範囲は、その後、x32デバイスに正式に適用されるように拡張されます。 、および高密度デバイスも同様です。」

組織

PC3200は、帯域幅3,200 MB / sのDDR-400チップを使用して200MHzで動作するように設計されたDDRSDRAMです。PC3200メモリはクロックの立ち上がりエッジと立ち下がりエッジの両方でデータを転送するため、その実効クロックレートは400MHzです。

1 GB PC3200非ECCモジュールは、通常、16個の512 Mビットチップで構成され、各側に8個(512 Mビット×16チップ)/(8ビット(バイトあたり))= 1,024MBです。1 GBのメモリモジュールを構成する個々のチップは、通常2 26個の8ビットワードとして編成され、通常は64M×8として表されます。この方法で製造されたメモリは低密度RAMであり、通常、PC3200DDR-400メモリを指定するマザーボードと互換性が

世代

DDR(DDR1)はDDR2 SDRAMに取って代わられました。これは、より高いクロック周波数と2倍のスループットに変更が加えられていますが、DDRと同じ原理で動作します。DDR2と競合したのはRambusXDRDRAMでし た。DDR2は、コストとサポートの要因により支配的でした。次に、DDR2はDDR3 SDRAMに取って代わられました。これにより、バス速度の向上と新機能により高いパフォーマンスが提供されました。DDR3はDDR4SDRAMに取って代わられました。DDR4SDRAMは、2011年に最初に製造され、その標準はまだ流動的であり(2012)、アーキテクチャが大幅に変更されています。

DDRのプリフェッチバッファの深さは2(ビット)ですが、DDR2は4を使用します。DDR2の実効クロックレートはDDRよりも高いですが、主に最初のDDR2モジュールのレイテンシが高いため、初期の実装では全体的なパフォーマンスは向上しませんでした。DDR2は、レイテンシの低いモジュールが利用可能になったため、2004年末までに有効になり始めました。

メモリメーカーは、内部速度の制限により、400 MHzを超える実効転送速度(つまり、400 MT / sおよび200MHzの外部クロック)でDDR1メモリを大量生産することは実用的ではないと述べました。DDR2は、DDR1と同様の内部クロックレートを利用して、DDR1が中断したところをピックアップしますが、400MHz以上の実効転送レートで使用できます。DDR3の進歩により、プリフェッチ深度を再び2倍にすることで、内部クロックレートを維持しながら、より高い実効転送レートを提供する機能が拡張されました。

DDR4 SDRAMは、16バンク、x4 / x8の各バンクグループに4バンクの4バンクグループ、およびx16 DRAMの各バンクグループに4バンクの2バンクグループとして内部構成された高速ダイナミックランダムアクセスメモリです。 。DDR4 SDRAMは、8nプリフェッチアーキテクチャを使用して高速動作を実現します。8 nプリフェッチアーキテクチャは、I / Oピンでクロックサイクルごとに2つのデータワードを転送するように設計されたインターフェイスと組み合わされています。DDR4 SDRAMの単一の読み取りまたは書き込み操作は、内部DRAMコアでの単一の8 nビット幅の4クロックデータ転送と、I / Oでの8つの対応するnビット幅の半クロックサイクルデータ転送で構成されます。ピン。

RDRAMはDDRSDRAMの特に高価な代替品であり、ほとんどのメーカーはチップセットからのサポートを中止しました。DDR1メモリの価格は2008年第2四半期以降大幅に上昇しましたが、DDR2の価格は下落しました。2009年1月、1 GBDDR1は1GB DDR2よりも2〜3倍高価でした。

DDRSDRAM世代の比較

名前 発売年

チップ バス 電圧(V)

ピン

Gen 標準 クロックレート(MHz)

サイクル時間(ns)

プリフェッチ_ クロックレート(MHz)

転送速度(MT / s)

帯域幅(MB /秒)

DIMM SO- DIMM Micro- DIMM

DDR DDR-200 2001〜2005 100 10 2n 100 200 1600 2.5 184 200 172

DDR-266 133 7.5 133 266 2133⅓

DDR-333 166⅔ 6 166⅔ 333 2666⅔

DDR-400 200 5 200 400 3200 2.62.6

DDR2 DDR2-400 2006〜 2010年 100 10 4n 200 400 3200 1.8 240 200 214

DDR2-533 133⅓ 7.5 266⅔ 533⅓ 4266⅔

DDR2-667 166⅔ 6 333⅓ 666⅔ 5333⅓

DDR2-800 200 5 400 800 6400

DDR2-1066 266⅔ 3.75 533⅓ 1066⅔ 8533⅓

DDR3 DDR3-800 2011〜 2015年 100 10 8n 400 800 6400 1.5 / 1.35 240 204 214

DDR3-1066 133⅓ 7.5 533⅓ 1066⅔ 8533⅓

DDR3-1333 166⅔ 6 666⅔ 1333⅓ 10666⅔

DDR3-1600 200 5 800 1600 12800

DDR3-1866 233⅓ 4.29 933⅓ 1866⅔ 14933⅓

DDR3-2133 266⅔ 3.75 1066⅔ 2133⅓ 17066⅔

DDR4 DDR4-1600 2016〜 2020年 200 5 8n 800 1600 12800 1.2 / 1.05 288 260 –

DDR4-1866 233⅓ 4.29 933⅓ 1866⅔ 14933⅓

DDR4-2133 266⅔ 3.75 1066⅔ 2133⅓ 17066⅔

DDR4-2400 300 3⅓ 1200 2400 19200

DDR4-2666 333⅓ 3 1333⅓ 2666⅔ 21333⅓

DDR4-2933 366⅔ 2.73 1466⅔ 2933⅓ 23466⅔

DDR4-3200 400 2.5 1600 3200 25600

DDR5 DDR5-3200 2021〜2025 200 5 16n 1600 3200 25600 1.1 288

DDR5-3600 225 4.44 1800 3600 28800

DDR5-4000 250 4 2000 4000 32000

DDR5-4800 300 3⅓ 2400 4800 38400

DDR5-5000 312½ 3.2 2500 5000 40000

DDR5-5120 320 3⅛ 2560 5120 40960

DDR5-5333 333⅓ 3 2666⅔ 5333⅓ 42666⅔

DDR5-5600 350 2.86 2800 5600 44800

DDR5-6400 400 2.5 3200 6400 51200

モバイルDDR LPDDR MDDRは、一部の企業がMobile DDR SDRAMに使用する頭字語であり、携帯電話、ハンドヘルド、デジタルオーディオプレーヤーなどの一部のポータブル電子デバイスで使用されるメモリの一種です。電圧供給の低減や高度なリフレッシュオプションなどの技術により、モバイルDDRはより高い電力効率を実現できます。

も参照してください

完全にバッファリングされたDIMM

コンピュータデータストレージの一種であるECCメモリ

デバイス帯域幅のリスト

シリアルプレゼンス検出

参考文献

^ “”Samsung 30 nm GreenPC3-12800ロープロファイル1.35VDDR3レビュー””。TechPowerUp。2012年3月8日。

^ ab 「SamsungElectronicsは超高速16MDDRSGRAMを搭載しています」。サムスン電子。サムスン。1998年9月17日。

^ “サムスンは世界初のDDR3メモリプロトタイプを実証します”。Phys.org。2005年2月17日。

^ WaybackMachineで2008年8月21日にアーカイブされたNorthwestLogic DDRPhyデータシート

^ 「ダイレクトクロッキング技術を使用したメモリインターフェイスデータキャプチャ(ザイリンクスアプリケーションノート)」(PDF)。xilinx.com。

^ B。ジェイコブ; SW Ng; DT Wang(2008)。メモリシステム:キャッシュ、DRAM、ディスク。モーガンカウフマン。p。333. ISBN 9780080553849。CS1 maint:作成者パラメーターを使用します(リンク) ^ HLカルター; CHスタッパー; J.Eバース; J。ディロレンツォ; CEドレイク; JAフィフィールド; GAケリー; SCルイス; WB van der Hoeven; JA Jankosky(1990)。「10nsのデータレートとオンチップECCを備えた50nsの16MbDRAM」。IEEE Journal of Solid-StateCircuits。25(5):1118。Bibcode:1990IJSSC..25.1118K。土井:10.1109 /4.62132。 CS1 maint:作成者パラメーターを使用します(リンク) ^ 「SamsungElectronicsはDDR / SDR製造オプションを備えた最初の128MbSDRAMを開発しました」。サムスン電子。サムスン。1999年2月10日。

^ 「歴史:1990年代」。SKハイニックス。

^ 「DDRSDRAMコントローラーとの愛/憎しみの関係」。

^ 「Iwillは最初のDDRマザーボードを明らかにします-PCStats.com」。www.pcstats.com 。2019-09-09を取得しました。

^ サイクルタイムは、I / Oバスクロック周波数の逆数です。たとえば、1 /(100 MHz)=クロックサイクルあたり10ns。

^ 「ダブルデータレート(DDR)SDRAM標準-JEDEC」。www.jedec.org。

^ 「PC-2100(DDR-266)、PC-2700(DDR-333)、およびPC-3200(DDR-400)の違いは何ですか?」。Micron Technology、Inc. 2013年12月3日にオリジナルからアーカイブされました。

^ Mike Chin:6台のPC内の配電。

^ ミクロン:ウェイバックマシンで2016年1月26日にアーカイブされたシステム電力計算機

^ 「低密度vs高密度メモリモジュール」。ebay.com。2012-03-03にオリジナルからアーカイブされました。

^ http://www.jedec.org/download/search/JESD79F.pdfダブルデータレート(DDR)SDRAM仕様(リリースF) ^ 「バイトあたりのRAMメモリアクセス」。スーパーユーザー。

^ DDR2 vs. DDR:ウェイバックマシンで2006年11月21日にアーカイブされたリベンジ

^ 「DDR4SDRAM標準JESD79-4B」。

外部リンク”