NAND_gate

入力

出力あ B

ナンドB0 0 1 0 1 1 1 0 1 00 01 02

デジタル エレクトロニクスでは、NAND ゲート( NOT-AND ) は、すべての入力が真の場合にのみ偽の出力を生成する論理ゲートです。したがって、その出力はAND ゲートの出力を補完します。LOW (0) 出力は、ゲートへのすべての入力が HIGH (1) の場合にのみ発生します。いずれかの入力が LOW (0) の場合、HIGH (1) 出力が発生します。NAND ゲートは、トランジスタと接合ダイオードを使用して作成されます。De Morgan の法則により、2 入力 NAND ゲートの論理は、 A • B = A + Bとして表すことができ、NAND ゲートはインバータとそれに続くOR ゲートに相当します。

4 つの NAND を含む TTL 7400 チップ。追加の 2 つのピンは電源 (+5 V) を供給し、グランドに接続します

NANDゲートは、NANDゲートの組み合わせを使用して任意のブール関数を実装できるため、重要です。この特性は機能的完全性と呼ばれます。このプロパティはNOR ゲートと共有されます。特定の論理回路を使用するデジタル システムは、NAND の機能の完全性を利用します。

関数NAND( a 1 , a 2 , …, a n )は、NOT( a 1 AND a 2 AND … AND a n ) と論理的に同等です。

A NAND B を表す 1 つの方法は、次のとおりです。あ ∧ B ¯

{ {overline {Aland B}}}

、ここで記号 ∧ { {land}}

は AND を表し、バーはその下の式の否定を表します。つまり、単純に ¬ ( あ∧ B )

{ { neg (Aland B)}} . 2 つ以上の入力を持つ NAND ゲートは、トランジスタ – トランジスタ ロジック、CMOS、およびその他のロジック ファミリの集積回路として利用できます。

コンテンツ

1 シンボル

2 ハードウェアの説明とピン配列

2.1 CMOS バージョン

2.1.1 可用性

3 実装

4 機能の完全性

5 こちらもご覧ください

6 参考文献

7 外部リンク

シンボル

NAND ゲートには 3 つのシンボルがMIL/ ANSIシンボル、IECシンボル、および古い回路図に見られる非推奨のDINシンボルです。詳細については、論理ゲート記号を参照してNAND ゲートの ANSI 記号は、反転バブルが接続された標準の AND ゲートです。

MIL/ANSI 記号 IEC 記号 DIN記号

ハードウェアの説明とピン配列

NANDゲートは基本的な論理ゲートであり、 TTLおよびCMOS ICで認識されています。

CMOS タイプ 4011 集積回路の NAND ゲートの図。

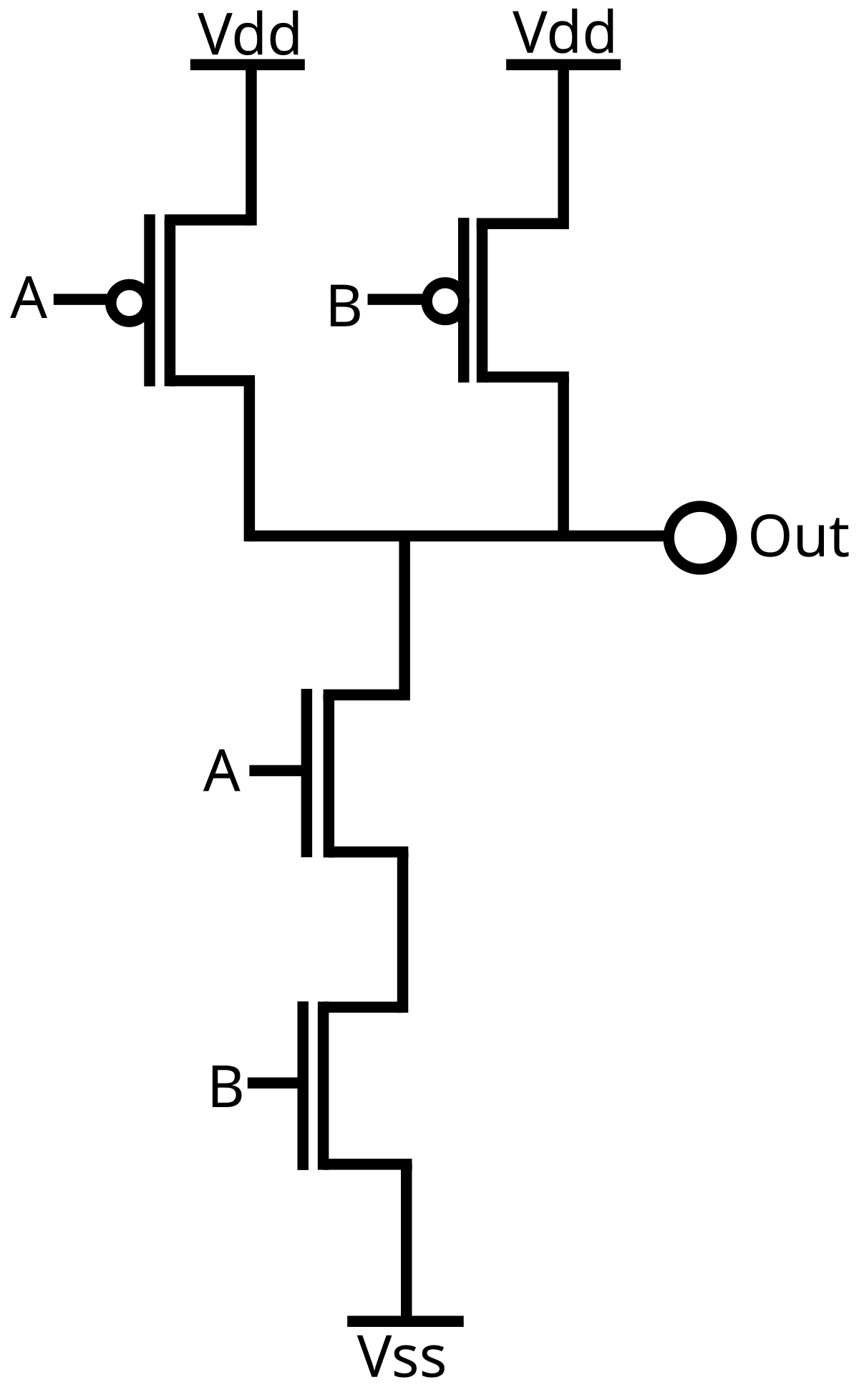

CMOS バージョン

標準の4000 シリーズのCMOS ICは 4011 で、これには 4 つの独立した 2 入力 NAND ゲートが含まれています。

可用性

これらのデバイスは、Fairchild Semiconductor、Philips、Texas Instrumentsなど、ほとんどの半導体メーカーから入手できます。これらは通常、スルーホールDILとSOICフォーマットの両方で入手できます。データシートは、ほとんどのデータシート データベースで簡単に入手できます。

標準の 2、3、4、および 8 入力 NAND ゲートが利用可能です。 CMOS 4011: クワッド 2 入力 NAND ゲート

4023: トリプル 3 入力 NAND ゲート

4012: デュアル 4 入力 NAND ゲート

4068: モノラル 8 入力 NAND ゲート TTL 7400: クワッド 2 入力 NAND ゲート

7410: トリプル 3 入力 NAND ゲート

7420: デュアル 4 入力 NAND ゲート

7430: モノラル 8 入力 NAND ゲート

実装

NMOS NAND ゲート

PMOS NAND ゲート

CMOS NAND ゲート

TTL NAND ゲート

CMOS NAND の物理レイアウト

NXP Semiconductors製の74AHC00Dクワッド2入力NANDゲートのダイ

集積回路内の 4 つの NAND ゲートのシリコン実装

機能の完全性

NAND ロジック

NAND ゲートは、 NOR ゲートと共通の機能的完全性を備えています。つまり、他の論理機能 (AND、OR など) は、NAND ゲートのみを使用して実装できます。 NAND ゲートのみを使用してプロセッサ全体を作成できます。複数のエミッタトランジスタを使用する TTL ICでは、NOR ゲートよりも少ないトランジスタしか必要としません。

NOR ゲートも機能的に完全であるため、特定の NAND ゲートが利用できない場合は、NOR ロジックを使用してNORゲートから作成できます。

ご希望のゲート

NOR建設

こちらもご覧ください

シェファーストローク

AND ゲート

OR ゲート

NOTゲート

NOR ゲート

XOR ゲート

XNOR ゲート

NOR ロジック

ブール代数

フラッシュメモリー

参考文献

^ Mano、M. Morris、Charles R. Kime. ロジックとコンピュータ設計の基礎、第 3 版。プレンティス ホール、2004 年。73.

外部リンク

TTL NAND および AND ゲート– 回路のすべて

![]()

・コモンズには、NAND ゲートに関連するメディアが · “