NAND_logic

、NAND ゲートだけを使用して他の論理ゲートを構築するという意味での NAND 論理について説明します。NAND ゲートについては、 NANDゲート を参照して純粋に論理的な意味での NAND については、論理 NANDを参照して一般的な論理ゲートについては、論理ゲートを参照して

NAND ブール関数には、機能の完全性という特性がこれは、ブール式は、 NAND演算のみを使用する同等の式で再表現できることを意味します。例えば、関数NOT(x)はNAND(x,x)と同等に表現され得る。これは、デジタル電子回路の分野では、NAND ゲートだけを使用して任意のブール関数を実装できることを意味します。

これの数学的証明は、1913 年にHenry M. ShefferによってAmerican Mathematical Society のトランザクション(Sheffer 1913) で公開されました。同様のケースがNOR 関数にも当てはまり、これをNOR ロジックと呼びます。

コンテンツ 1 NAND 2 NANDゲートを使って他のゲートを作る

2.1 いいえ 2.2 と 2.3 また 2.4 または 2.5 XOR 2.6 XNOR

3 マルチプレクサ

4 デマルチプレクサ

5 こちらもご覧ください

6 外部リンク

7 参考文献

NAND

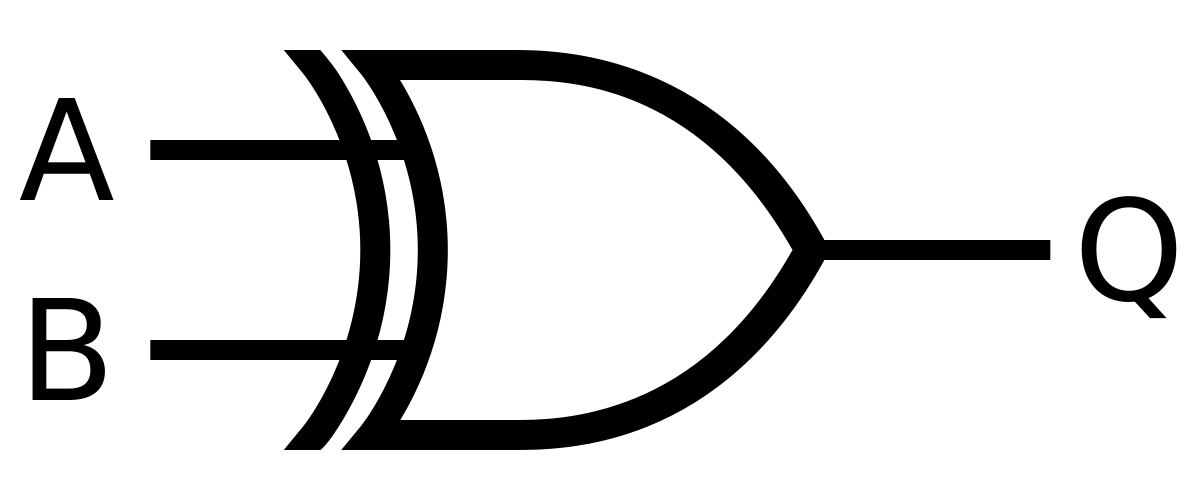

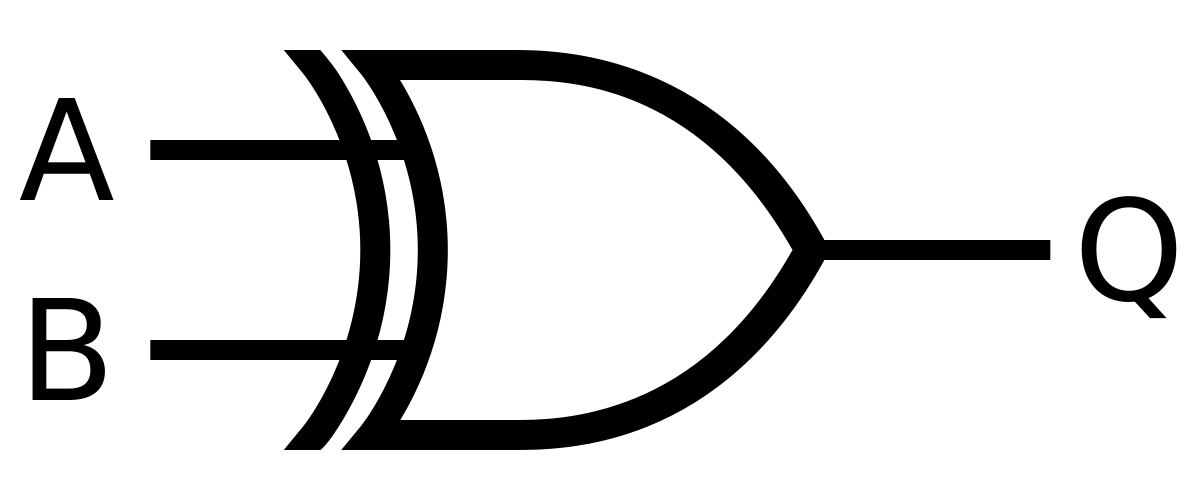

NAND ゲート

NAND ゲートは反転AND ゲートです。次の真理値表が

Q = A NAND B

真理値表

入力 A

入力 B

出力 Q0 0 1 0 1 1 1 0 1 00 01 02

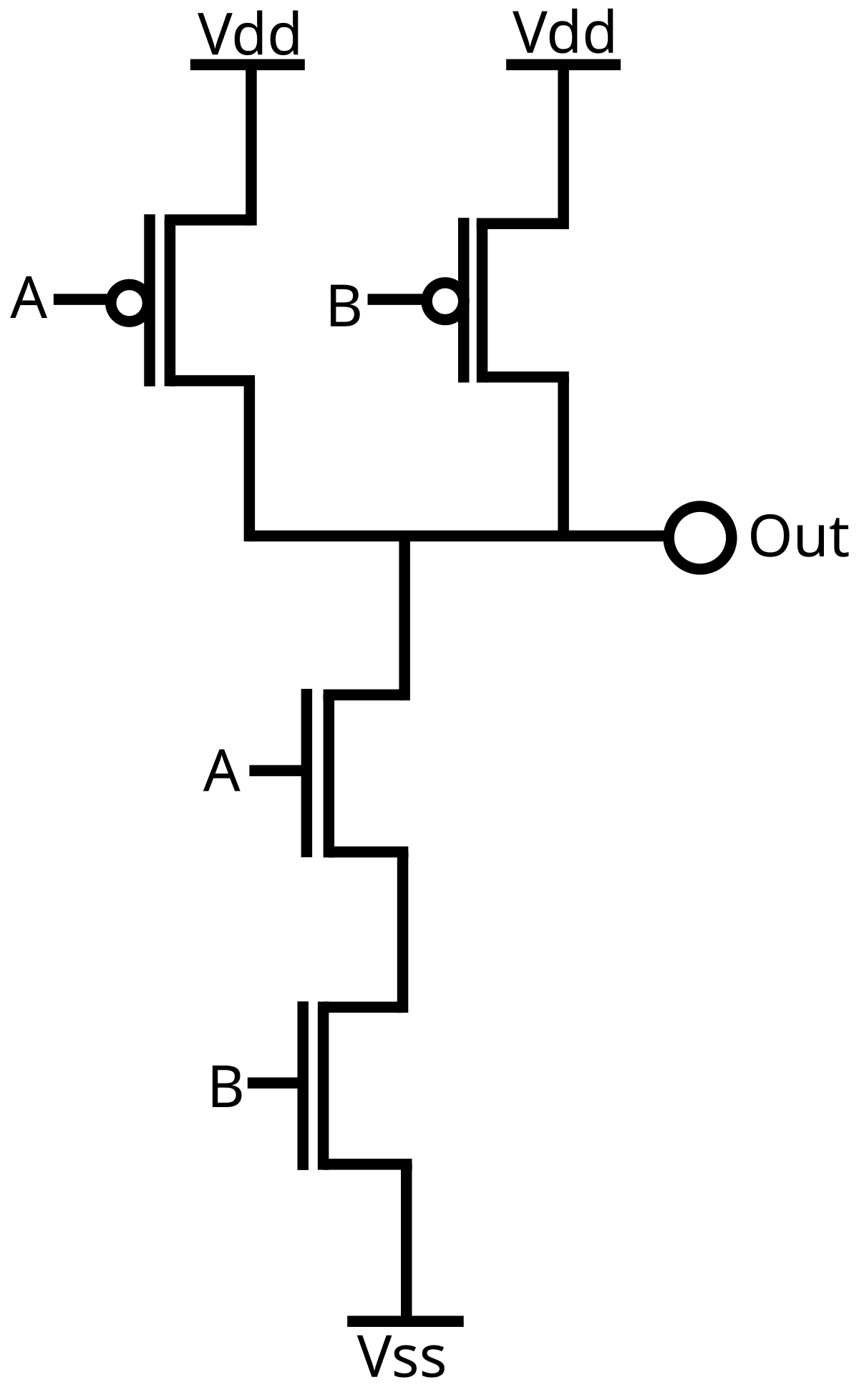

CMOSトランジスタのNAND 素子。V ddは正の電圧を表します。

CMOSロジックでは、A 入力と B 入力の両方が High の場合、両方のNMOS トランジスタ(図の下半分) が導通し、PMOSトランジスタ (上半分) はどちらも導通せず、その間に導通経路が確立されます。出力と Vss (グランド) を接続し、出力をローにします。A 入力と B 入力の両方が Low の場合、NMOS トランジスタはどちらも導通しませんが、PMOS トランジスタは両方とも導通し、出力と Vdd (電圧源) の間に導通経路が確立され、出力が High になります。A または B 入力のいずれかがローの場合、NMOS トランジスタの 1 つが導通せず、PMOS トランジスタの 1 つが導通し、出力と Vdd (電圧源) の間に導通経路が確立され、出力がハイになります。Low 出力になる 2 つの入力の唯一の構成は、両方が High の場合であるため、この回路は NAND (NOT AND) 論理ゲートを実装します。

NANDゲートを使って他のゲートを作る

NANDゲートはユニバーサルゲートです。つまり、他のゲートはNANDゲートの組み合わせとして表すことができます。

いいえ

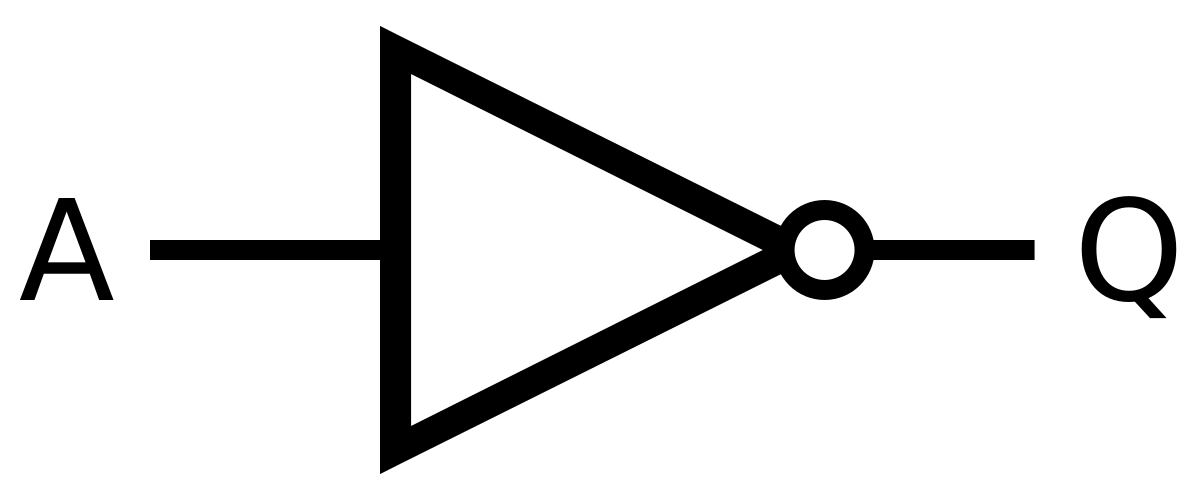

「 NOT ゲート

」も参照

NOT ゲートは、NAND ゲートの入力を結合することによって作成されます。NAND ゲートは、AND ゲートの後に NOT ゲートが続くことと同等であるため、NAND ゲートの入力を結合すると、NOT ゲートだけが残ります。

希望のNOTゲート

NAND構造

Q = NOT( A )= A NAND A

真理値表

入力 A

出力 Q0 1 1

0

と

参照: AND ゲート

AND ゲートは、以下に示すように、NAND ゲートの出力を反転することによって作成されます。

望ましい AND ゲート

NAND構造

Q = A AND B= ( A NAND B ) NAND ( A NAND B )

真理値表

入力 A

入力 B

出力 Q0 0 0 0 1 0 1 0 0 00 01

1

また

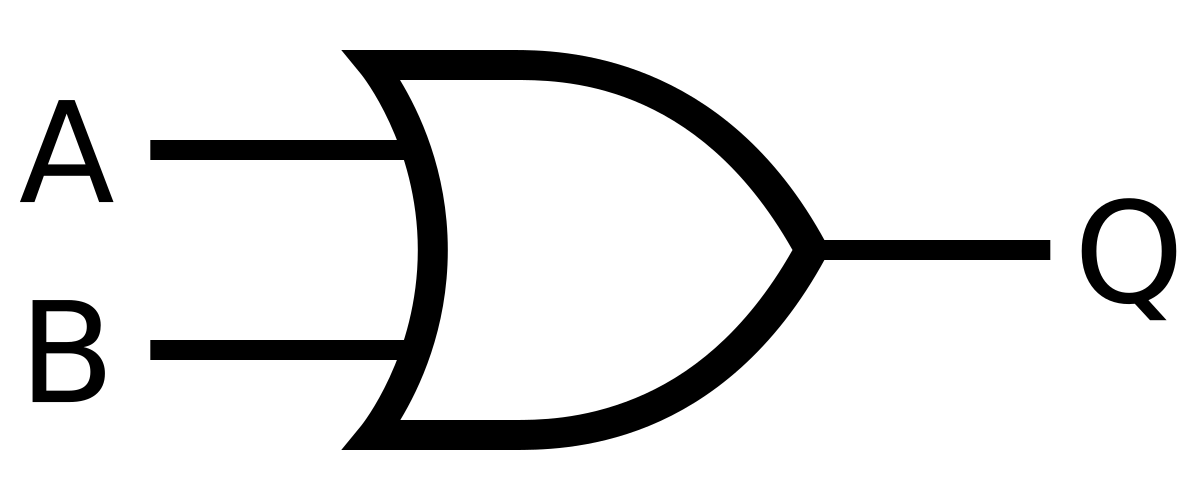

参照: OR ゲート

NAND ゲートの真理値表を調べたり、ド モルガンの法則を適用したりすると、入力のいずれかが 0 の場合、出力が 1 になることがわかります。ただし、OR ゲートになるには、出力が 1 でなければなりません。いずれかの入力が 1 の場合。したがって、入力が反転されている場合、ハイ入力はハイ出力をトリガーします。

希望する OR ゲート

NAND構造

Q = AまたはB= ( A NAND A ) NAND ( B NAND B )

真理値表

入力 A

入力 B

出力 Q0 0 0 0 1 1 1 0 1 00 01

1

または

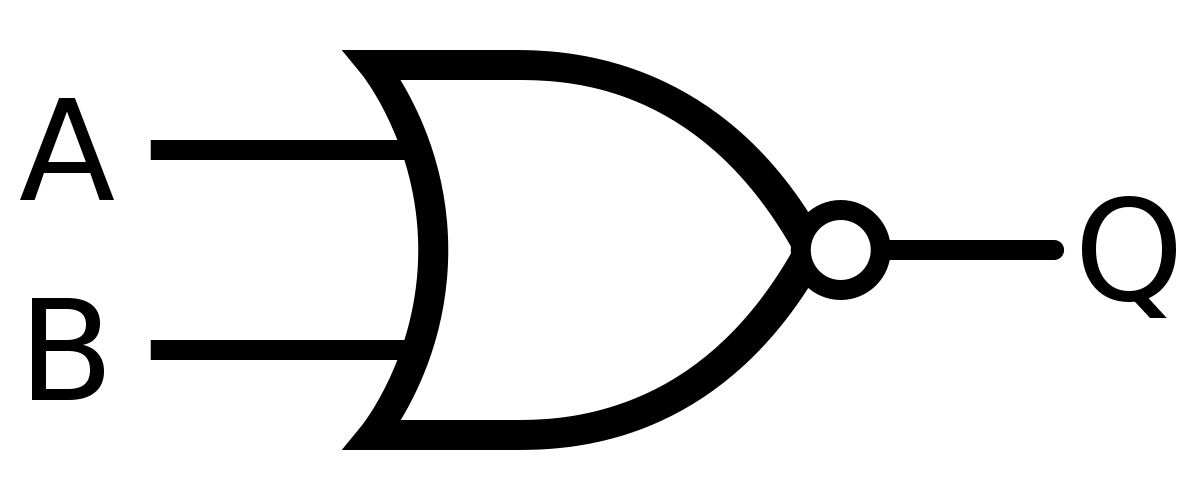

「 NOR ゲート

」も参照

NOR ゲートは反転出力を持つ OR ゲートです。入力 A も入力 B もハイでない場合、出力はハイです。

目的の NOR ゲート

NAND構造

Q = A NOR B= [ ( A NAND A ) NAND ( B NAND B ) ] NAND [ ( A NAND A ) NAND ( B NAND B ) ]

真理値表

入力 A

入力 B

出力 Q0 0 1 0 1 0 1 0 0 00 01

0

XOR

参照: XOR ゲート

XOR ゲートは、以下に示すように 4 つの NAND ゲートを接続することによって作成されます。この構造では、単一の NAND ゲートの 3 倍の伝搬遅延が発生します。

目的の XOR ゲート

NAND構造

Q = A XOR B= [ A NAND ( A NAND B ) ] NAND [ B NAND ( A NAND B ) ]

真理値表

入力 A

入力 B

出力 Q0 0 0 0 1 1 1 0 1 00 01 02

あるいは、XOR ゲートは、論理和正規形を考慮して作成されます。あ ⋅ B ¯+あ ¯

⋅ B { Acdot {overline {B}}+{overline {A}}cdot B}

、ド・モルガンの法則から、NAND ゲートは反転入力 OR ゲートであることに注意してこの建設では、4 つではなく 5 つのゲートを使用します。

希望のゲート

NAND構造

Q = A XOR B= [ B NAND ( A NAND A ) ] NAND [ A NAND ( B NAND B ) ]

XNOR

参照: XNOR ゲート

XNOR ゲートは、論理和正規形を考慮して作成されます。あ ⋅ B + あ ¯

⋅B ¯

{ Acdot B+{overline {A}}cdot {overline {B}}}

、ド・モルガンの法則から、NAND ゲートは反転入力 OR ゲートであることに注意してこの構造では、1 つの NAND ゲートの 3 倍の伝搬遅延が発生し、5 つのゲートを使用します。

目的の XNOR ゲート

NAND構造

Q = A XNOR B= [ ( A NAND A ) NAND ( B NAND B ) ] NAND ( A NAND B )

入力 A

入力 B

出力 Q0 0 1 0 1 0 1 0 0 00 01 02

または、XOR ゲートの 4 ゲート バージョンをインバータと共に使用することもできます。この構成では、単一の NAND ゲートの (3 倍ではなく) 4 倍の伝搬遅延が

希望のゲート

NAND構造

Q = A XNOR B= { [ A NAND ( A NAND B ) ] NAND [ B NAND ( A NAND B ) ] } NAND { [ A NAND ( A NAND B ) ] NAND [ B NAND ( A NAND B ) ] }

マルチプレクサ

マルチプレクサまたは MUX ゲートは、セレクタ ビットと呼ばれる入力の 1 つを使用して、データ ビットと呼ばれる他の 2 つの入力の 1 つを選択し、選択されたデータ ビットのみを出力する3 入力ゲートです。

目的の MUX ゲート

NAND構造

Q = OR ( B AND S )= [ A NAND ( S NAND S ) ] NAND ( B NAND S )

真理値表

入力 A

入力 B

選択する

出力 Q0 0 0 0 0 1 0 0 1 00 01 02 03

10 1 0 0 1 0 0 1 1 00 01 02 030 1 1 1

1

デマルチプレクサ

デマルチプレクサは、マルチプレクサとは逆の機能を実行します。単一の入力を取り、選択する出力を指定するセレクタ ビットに従って、2 つの可能な出力のいずれかにチャネルします。

目的の DEMUX ゲート

NAND構造

真理値表

入力

選択する

出力 A

出力 B0 0 0 0 1 0 1 0 0 00 01 02 031 0

1

こちらもご覧ください

NAND論理素子を生成するCMOSトランジスタ構造とチップ堆積形状

シェファー脳卒中- 別名

NOR ロジック。NANDゲートと同様に、NORゲートもユニバーサルゲートです。

機能の完全性

外部リンク

TTL NAND および AND ゲート- 回路のすべて

NAND ゲートから XOR を導出する手順。

NandGame – NAND ゲートのみを使用してコンピューターを構築するゲーム

参考文献

^ Nisan, N. & Schocken, S., 2005. In: From NAND to Tetris: Building a Modern Computer from First Principles. sl:The MIT Press、p. 20. 入手先: http://www.nand2tetris.org/chapters/chapter%2001.pdf 2017 年 1 月 10 日、Wayback Machineでアーカイブ

ランカスター、ドン(1974)。TTL クックブック(第 1 版)。インディアナ州インディアナポリス: ハワード・W・サムズ。pp.126–135 。_ ISBN 0-672-21035-5.

Sheffer, HM (1913)、「ブール代数の 5 つの独立した仮定のセット、論理定数への適用」、米国数学会のトランザクション、14 : 481–488、doi : 10.2307/1988701、JSTOR 1988701″