Via_(electronics)

集積回路のビアについては、シリコン貫通ビアを参照してください

Aを介して(ラテン語のための経路または方法)は、電気的接続における銅層の間の印刷回路基板。基本的に、ビアは2つ以上の隣接する層を貫通する小さなドリル穴です。穴は銅でメッキされており、銅層を分離する絶縁体を介して電気接続を形成します。

コンテンツ

1 プリント回路基板で

2 故障動作

3 ギャラリー

4 も参照してください

5 参考文献

6 外部リンク

プリント回路基板で

さまざまな種類のビア:( 1)

スルーホール。(2)ブラインドビア。(3)経由で埋められます。

灰色と緑色の層は非導電性ですが、薄いオレンジ色の層とビアは導電性です。

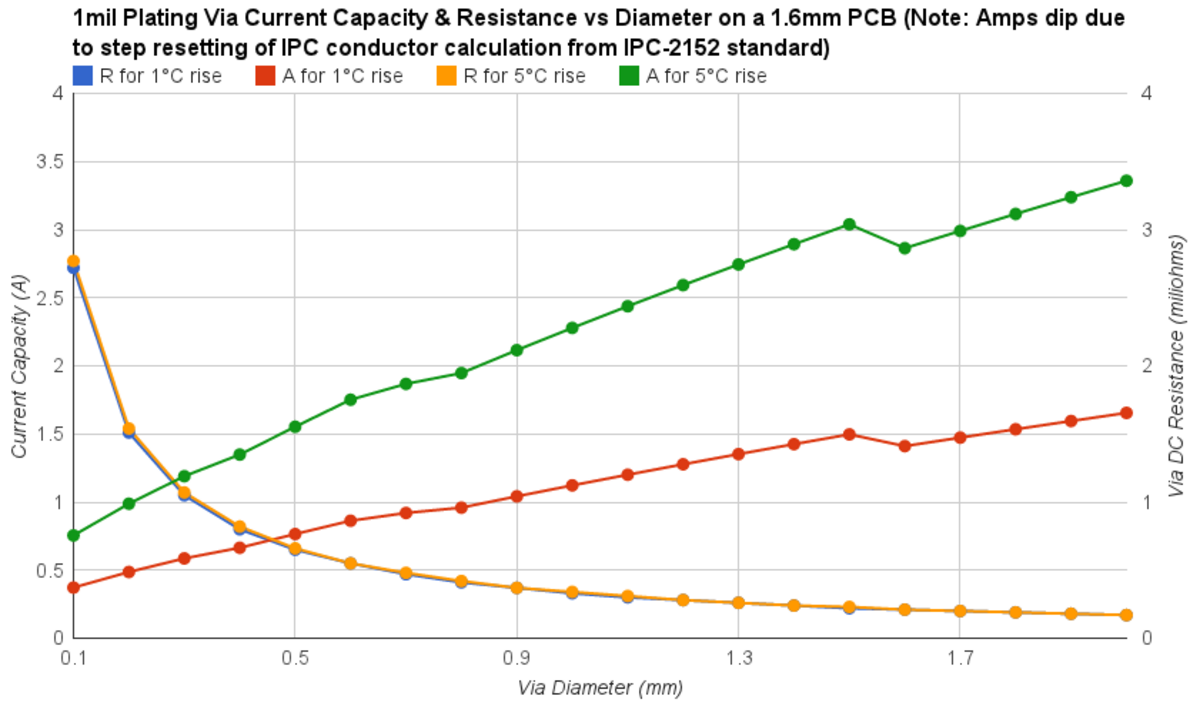

1.6mmPCBの電流容量と抵抗対直径を介した1milメッキを示すPCBビア電流容量チャート

プリント回路基板(PCB)設計、Aを介して電気的に基板スルーホールによって接続されている基板の異なる層に対応する位置に2つのパッドから成ります。穴は電気めっきによって導電性にされるか、チューブまたはリベットで裏打ちされます。高密度多層PCBにはマイクロビアが含まれる場合がブラインドビアはボードの片側にのみ露出しますが、埋め込みビアはどちらの表面にも露出せずに内部層を接続します。サーマルビアはパワーデバイスから熱を運び去り、通常、約12個のアレイで使用されます。

ビアは次のもので構成されます。

バレル—ドリル穴を埋める導電性チューブ

パッド—バレルの両端をコンポーネント、平面、またはトレースに接続します

アンチパッド—バレルとそれが接続されていない金属層の間のクリアランスホール

ビアは、PTVまたはメッキスルービアと呼ばれることもあり、メッキスルーホール(PTH)と混同しないでビアはPCB上の銅層間の相互接続として使用されますが、PTHは一般にビアよりも大きくなり、非SMT抵抗、コンデンサ、DIPパッケージICなどのコンポーネントリードを受け入れるためのメッキ穴として使用されます。PTHは、機械的接続用の穴としても使用できますが、ビアは使用できない場合がPTHの別の使用法は、PTHがボードの端に位置合わせされ、ボードがパネルからフライス盤で削られるときに半分にカットされるキャスタレーション穴として知られています。主な使用法は、1つのPCBをはんだ付けできるようにすることです。もう1つはスタック内にあり、ファスナーとしてもコネクタとしても機能します。

右図に3つの主要なビアを示します。PCBを作成する基本的な手順は次のとおりです。基板材料を作成し、それを層状に積み重ねます。ビアのめっきのスルードリル; フォトリソグラフィーとエッチングを使用した銅トレースパターニング。この標準的な手順では、可能なビア構成はスルーホールに限定されます。レーザーの使用などの深さ制御された穴あけ技術により、より多様なビアタイプが可能になります。(レーザードリルは、機械式ドリルが生成するよりも小さく、より正確に配置された穴にも使用できます。)PCBの製造は、通常、いわゆるコア、基本的な両面PCBから始まります。最初の2つを超えるレイヤーは、この基本的な構成要素から積み重ねられます。さらに2つの層がコアの下部から連続して積み重ねられている場合は、1-2ビア、1-3ビア、およびスルーホールを使用できます。各タイプのビアは、各スタッキング段階でドリルで作成されます。1つの層がコアの上に積み重ねられ、もう1つの層が下から積み重ねられる場合、可能なビア構成は1〜3、2〜3、およびスルーホールです。ユーザーは、PCBメーカーが許可しているスタッキング方法と可能なビアに関する情報を収集する必要がより安価なボードの場合、貫通穴のみが作成され、ビアに接触しないようになっている層にアンチパッド(またはクリアランス)が配置されます。

故障動作

うまく作られている場合、PCBビアは、銅メッキとPCBの間の面外方向(Z)での膨張と収縮の差により、主に故障します。この差動膨張と収縮は、銅めっきに周期的な疲労を引き起こし、最終的には亀裂の伝播と電気的な開回路をもたらします。さまざまな設計、材料、および環境パラメータが、この劣化の速度に影響を与えます。 堅牢性を介して保証するために、IPCは、障害までの時間の計算機を開発するラウンドロビン演習を後援しました。

ギャラリー

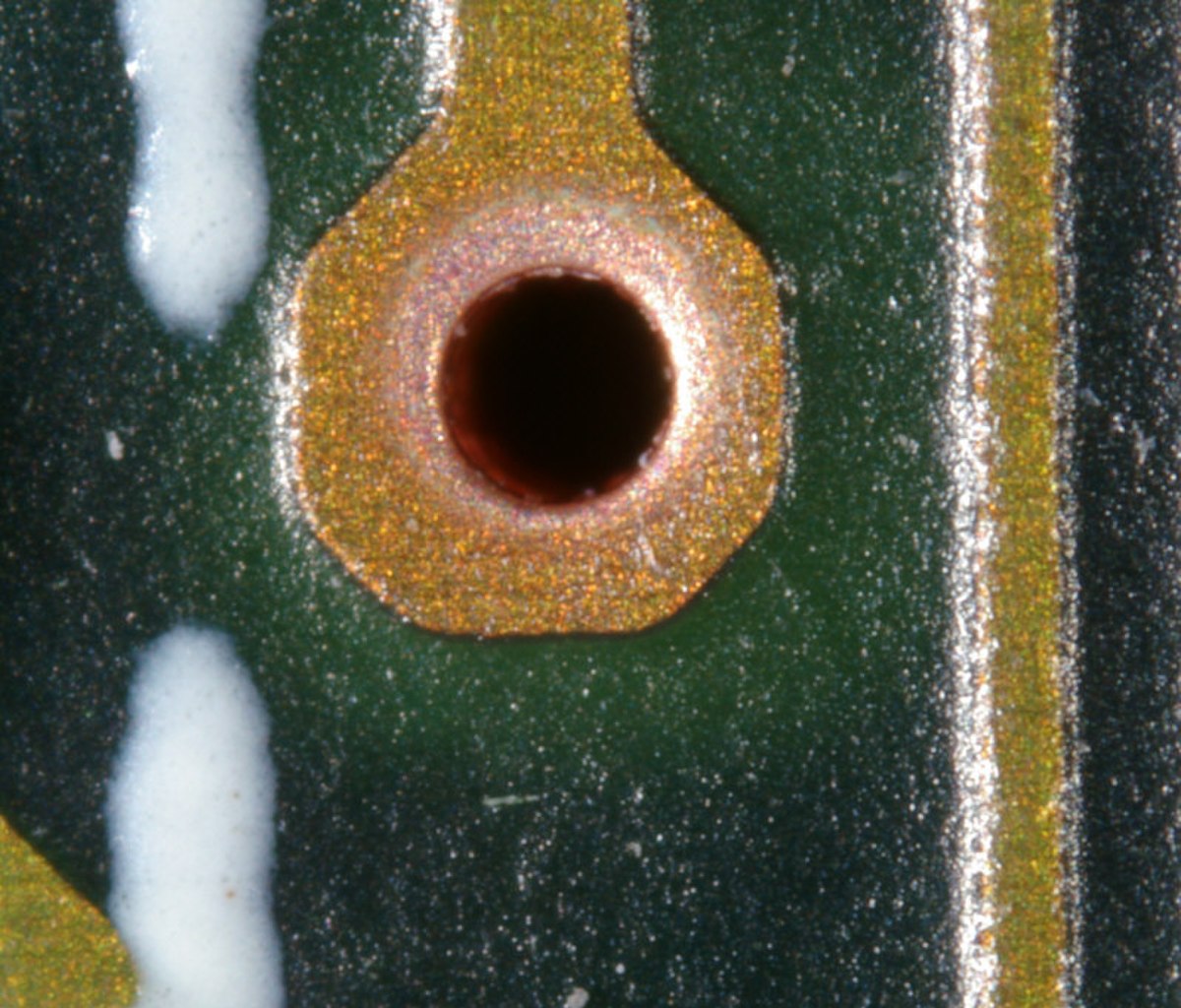

メッキスルーホール、このセクションでは、多層ボード上に8つあります(拡大)

CADの2層メッキ。ViasはEDAの配置を可能にします。最 下層–赤 最上層–青

メッキスルーホールのメッキ:上–上層下–下層

多層パーセプトロンの断面図

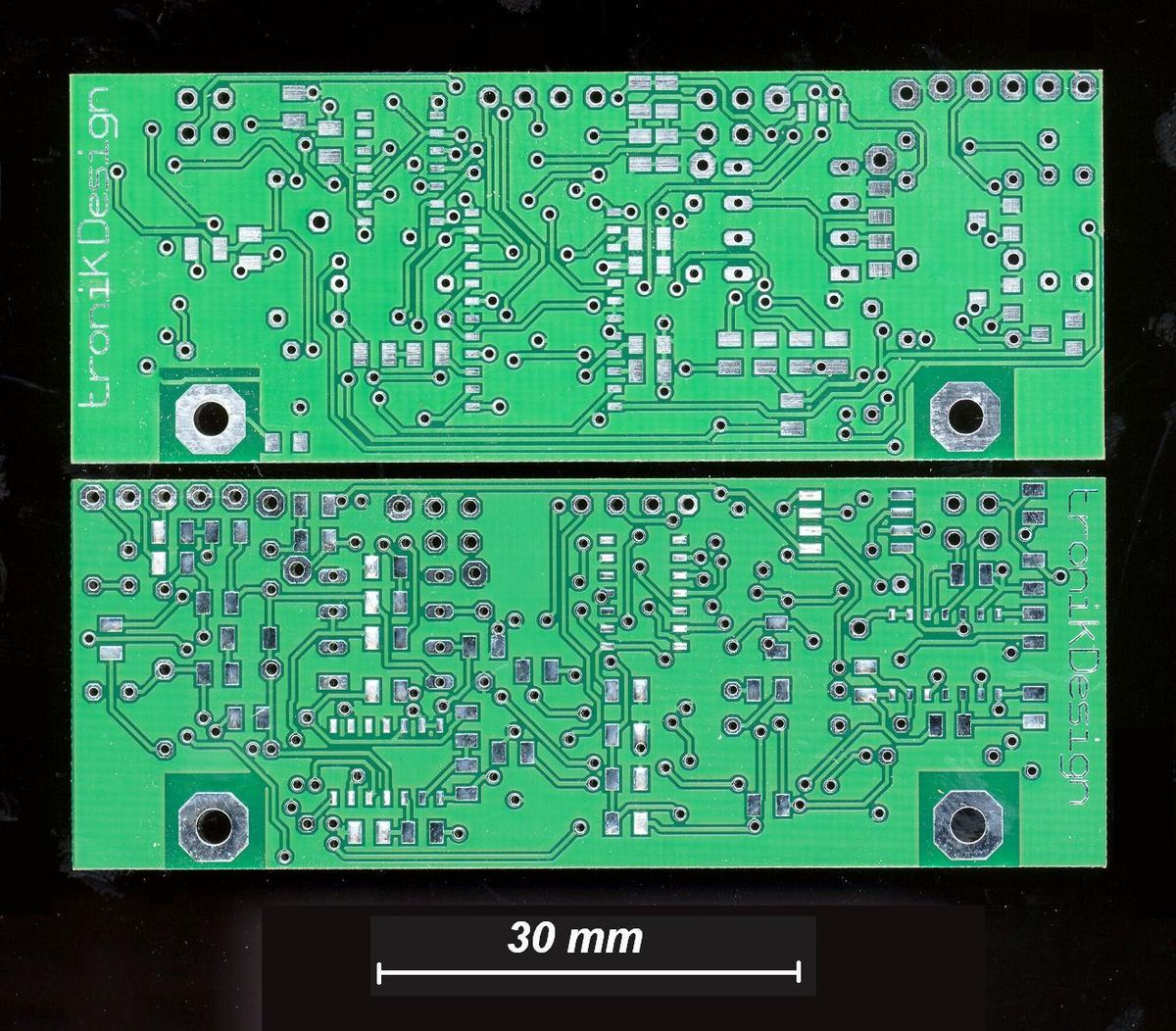

小さな金属の円はビアです

も参照してください

ウィキブックスの実用的な電子機器には、PCB Layout#Holesのトピックに関するページが

スルーホール技術(THT)

表面実装技術(SMT)

シリコン貫通電極(TSV)

フェンス経由

フィードスルー

参考文献

^ ええと、コアごとのスルーホール。より高価ですが、追加のコアとラミネーションステップを使用してブラインドビアまたは埋め込みビアを作成することは可能です。メッキを片側から目的の層までバックドリルして除去することも可能です。これにより、物理的な穴はスルーホールとして残りますが、電気的にはブラインドビアと同等になります。とは言うものの、PCBがブラインドビアと埋め込みビアを正当化するのに十分な層を必要とする場合は、とにかく(レーザードリルで穴を開けた)マイクロビアを必要とするほどしっかりと詰め込まれた十分に小さいトレースも使用している可能性が

^ 「PCB設計:熱ビアについての事実と神話の詳細」。

^ 「CastellatedHoles / Edge Plating PCB / Castellations」。ハイテック株式会社2011年アーカイブからオリジナルの2016年5月26日に。

^ C.ヒルマン、失敗によるプレートスルーの理解、グローバルSMTおよびパッケージング– 2013年11月、26〜28ページ、 https: //www.dfrsolutions.com/hubfs/Resources/services/Understanding_Plated_Through_Via_Failures.pdf? t = 1514473946162 ^ C. Hillman、Via Design and Fabricationによる信頼性の高いメッキ、 http://resources.dfrsolutions.com/White-Papers/Reliability/Reliable-Plated-Through-Via-Design-and-Fabrication1.pdf ^ 「メッキスルーホール(PTH)疲労計算機」。DfRソリューション。

外部リンク

「PCBビア設計のヒント」 (PDF)(テクニカルノート)。クイックテック。2014.EN-00417 。

「テンティング経由-バリエーションの概要」。WEオンライン。WürthElektronikGmbH&Co。KG。2014.プリント回路基板>レイアウト>デザインのヒント>テンティング。2017年12月18日にオリジナルからアーカイブされました。

「プラグイン経由-バリエーションの概要」。WEオンライン。WürthElektronikGmbH&Co。KG。2014.プリント回路基板>レイアウト>設計のヒント>プラグイン。2017年12月18日にオリジナルからアーカイブされました。

「ViaFilling-バリエーションの概要」。WEオンライン。WürthElektronikGmbH&Co。KG。2013.プリント回路基板>レイアウト>設計のヒント>充填。2017年12月18日にオリジナルからアーカイブされました。

「MicroviaFilling」。WEオンライン。WürthElektronikGmbH&Co。KG。2015.プリント回路基板>レイアウト>設計のヒント>マイクロビア充填。2017年12月18日にオリジナルからアーカイブされました。

ディングラー、クラウス; Musewski、Markus(2009-03-18)。「プラグゲン/プラグ」。FED-Wiki(ドイツ語)。ドイツ、ベルリン:Fachverband Elektronik-Design eV(FED)。2017年12月18日にオリジナルからアーカイブされました。

「高速チャネル設計のための最適化手法による」 (PDF)(アプリケーションノート)。1.0。アルテラ株式会社。2008年5月。AN-529-1.0。2017年12月18日にオリジナルからアーカイブ (PDF)。

チュー・ジュン(2017-04-11)。「制御された深さの穴あけ、または逆穴あけ」。Altium製品のオンラインドキュメント。アルティウム。2017年12月18日にオリジナルからアーカイブされました。

ラフヘッド、フィル(2017-05-30)。「未使用のパッドの取り外しとティアドロップの追加」。Altium製品のオンラインドキュメント。アルティウム。2017年12月18日にオリジナルからアーカイブされました。

ブルックス、ダグラスG。; Adam、Johannes(2017-02-09)、PCBトレースとビア温度:完全な分析(第2版)、CreateSpace Independent Publishing Platform、ISBN 978-1541213524″